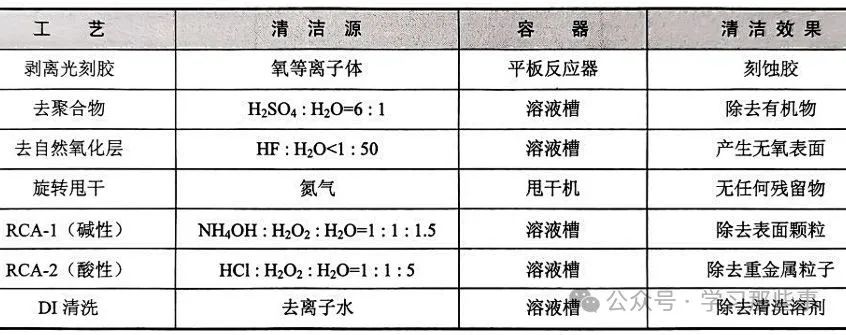

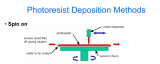

光刻工藝的主要流程和關(guān)鍵指標(biāo)

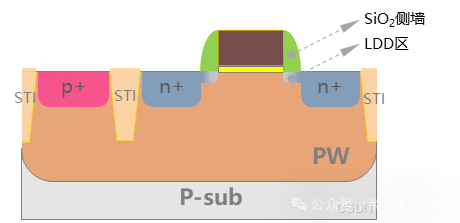

光刻工藝貫穿整個芯片制造流程的多次重復(fù)轉(zhuǎn)印環(huán)節(jié),對于集成電路的微縮化和高性能起著決定性作用。隨著半導(dǎo)....

封裝設(shè)計圖紙的基本概念和類型

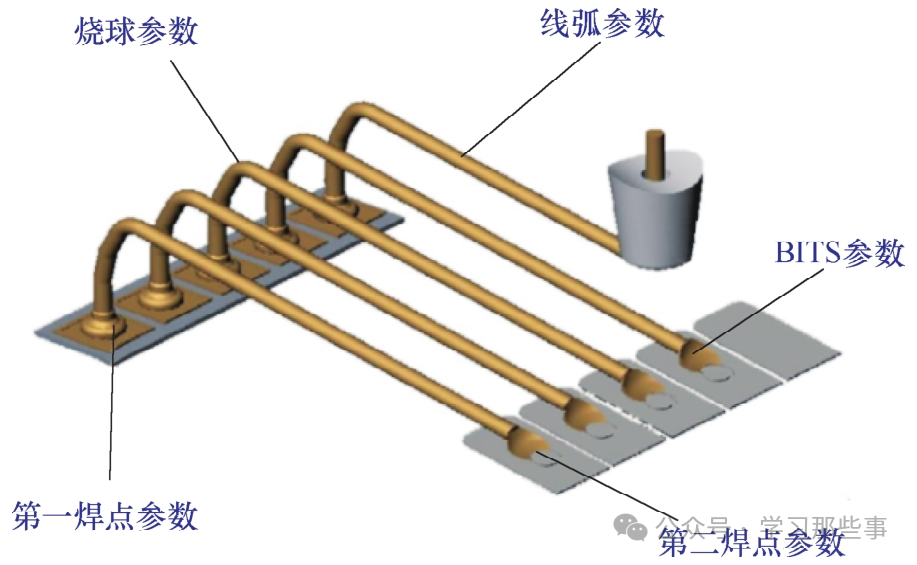

封裝設(shè)計圖紙是集成電路封裝過程中用于傳達封裝結(jié)構(gòu)、尺寸、布局、焊盤、走線等信息的重要文件。它是封裝設(shè)....

太赫茲無線通信介紹

無線通信系統(tǒng)從 1980 年代的第一代發(fā)展到最近的第五代 (5G),一直是推動這項技術(shù)在通信和我們?nèi)?...

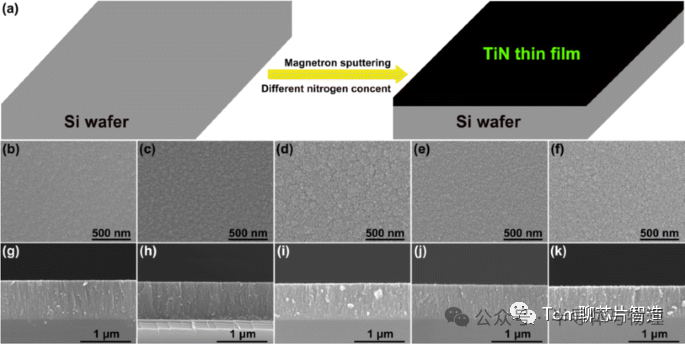

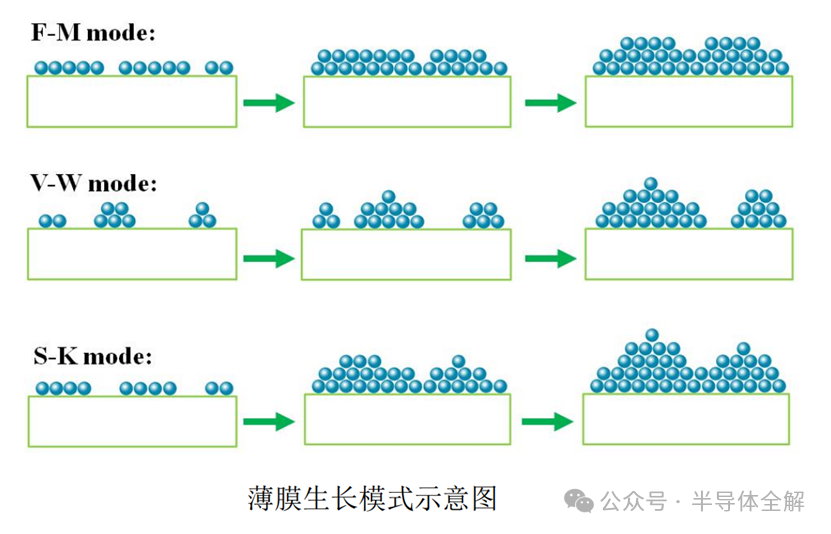

常見的幾種薄膜外延技術(shù)介紹

薄膜外延生長是一種關(guān)鍵的材料制備方法,其廣泛應(yīng)用于半導(dǎo)體器件、光電子學(xué)和納米技術(shù)領(lǐng)域。

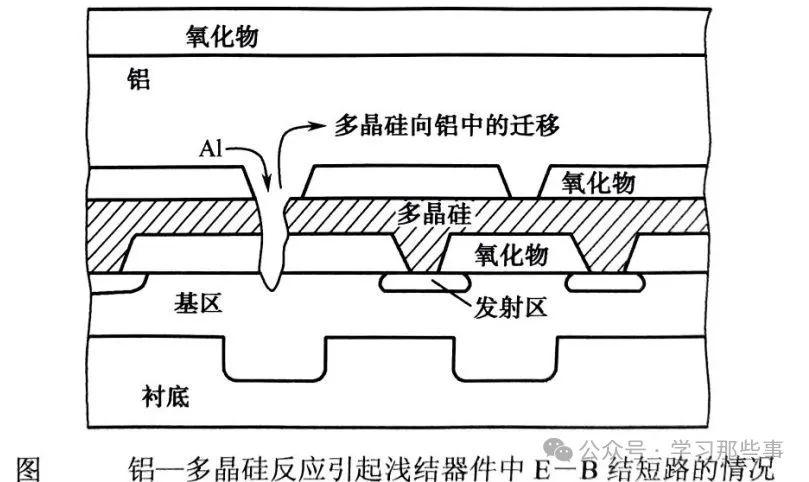

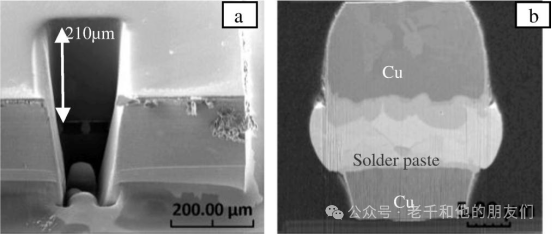

PFIB技術(shù)在半導(dǎo)體領(lǐng)域中的應(yīng)用

新一代封裝技術(shù)中出現(xiàn)了嵌入多個芯片的復(fù)雜系統(tǒng)設(shè)計。倒裝芯片和銅柱互連、多MEMS-IC系統(tǒng)以及新型傳....

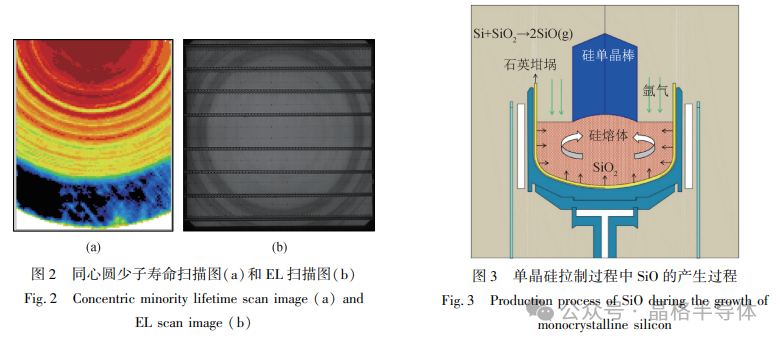

多晶硅錠定向凝固生長方法

鑄錠澆注法是較早出現(xiàn)的一種技術(shù),該方法先將硅料置于熔煉坩堝中加熱熔化,隨后利用翻轉(zhuǎn)機械將其注入模具內(nèi)....

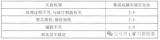

封裝基板設(shè)計的詳細(xì)步驟

封裝基板設(shè)計是集成電路封裝工程中的核心步驟之一,涉及將芯片與外部電路連接的基板(substrate)....

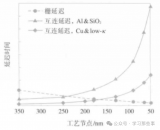

集成電路和光子集成技術(shù)的發(fā)展歷程

本文介紹了集成電路和光子集成技術(shù)的發(fā)展歷程,并詳細(xì)介紹了鈮酸鋰光子集成技術(shù)和硅和鈮酸鋰復(fù)合薄膜技術(shù)。