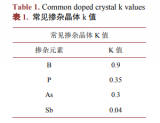

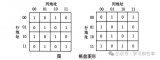

FPGA芯片的概念和結(jié)構(gòu)

FPGA(Field Programmable Gate Array,現(xiàn)場可編程門陣列),是一種可在....

簡單認識晶圓減薄技術(shù)

在半導(dǎo)體制造流程中,晶圓在前端工藝階段需保持一定厚度,以確保其在流片過程中的結(jié)構(gòu)穩(wěn)定性,避免彎曲變形....

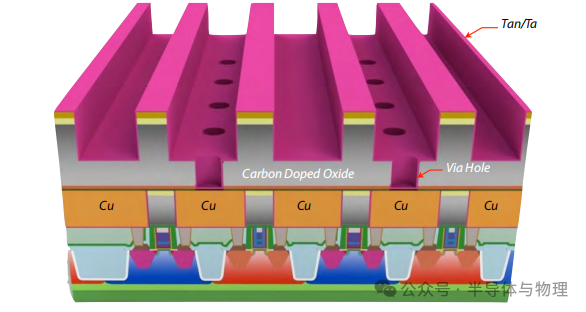

半導(dǎo)體電鍍工藝介紹

Plating(電鍍)是一種電化學(xué)過程,通過此過程在基片(wafer)表面沉積金屬層。在微電子領(lǐng)域,....

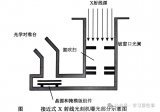

詳談X射線光刻技術(shù)

隨著極紫外光刻(EUV)技術(shù)面臨光源功率和掩模缺陷挑戰(zhàn),X射線光刻技術(shù)憑借其固有優(yōu)勢,在特定領(lǐng)域正形....

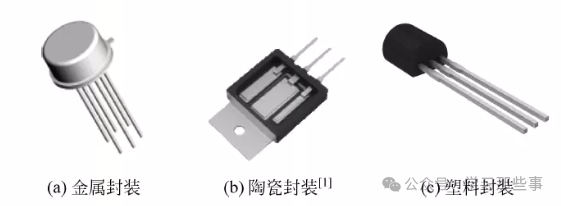

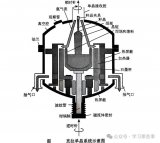

CPU Socket的基本結(jié)構(gòu)和工作原理

CPU Socket是連接中央處理單元(CPU)與計算機主板之間的關(guān)鍵部件,它充當著傳遞電信號、電源....

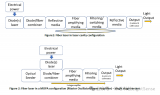

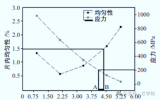

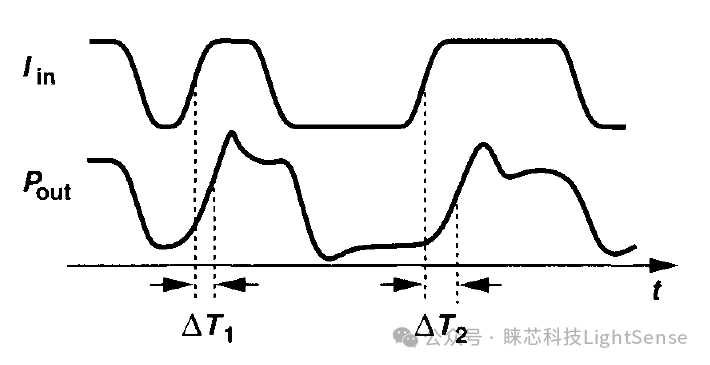

淺談光通信激光器的關(guān)鍵特性

當激光器導(dǎo)通時,開始產(chǎn)生自發(fā)輻射的光子直到載流子密度超過一個閾值。因而,產(chǎn)生受激輻射,也就是說,真實....

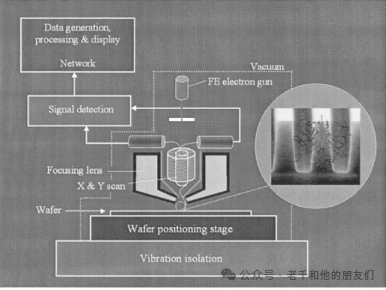

關(guān)鍵尺寸掃描電子顯微鏡技術(shù)解讀

計量學(xué)是推動當前及未來幾代半導(dǎo)體器件開發(fā)與制造的重要基石。隨著技術(shù)節(jié)點不斷縮小至100納米,甚至更小....

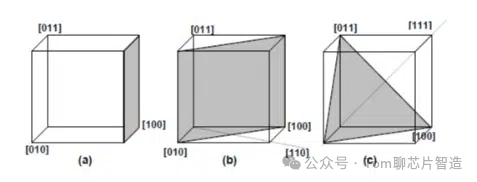

晶圓制備工藝與清洗工藝介紹

晶圓制備是材料科學(xué)、熱力學(xué)與精密控制的綜合體現(xiàn),每一環(huán)節(jié)均凝聚著工程技術(shù)的極致追求。而晶圓清洗本質(zhì)是....

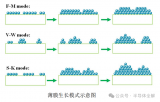

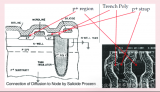

半導(dǎo)體選擇性外延生長技術(shù)的發(fā)展歷史

選擇性外延生長(SEG)是當今關(guān)鍵的前端工藝(FEOL)技術(shù)之一,已在CMOS器件制造中使用了20年....

一文詳解電子束光刻技術(shù)

本文系統(tǒng)梳理了直寫式、多電子束與投影式EBL的關(guān)鍵技術(shù)路徑,涵蓋掃描策略、束流整形、鄰近效應(yīng)校正與系....

FPGA芯片選型的核心原則

本文總結(jié)了FPGA選型的核心原則和流程,旨在為設(shè)計人員提供決策依據(jù),確保項目成功。

TSSG生產(chǎn)碳化硅的優(yōu)勢

微管是SiC晶體中極為有害的缺陷,哪怕數(shù)量極少,也會對SiC器件的性能產(chǎn)生毀滅性打擊。在傳統(tǒng)物理氣相....