鑄錠澆注法是較早出現(xiàn)的一種技術(shù),該方法先將硅料置于熔煉坩堝中加熱熔化���,隨后利用翻轉(zhuǎn)機械將其注入模具內(nèi)....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-13 14:41

?554次閱讀

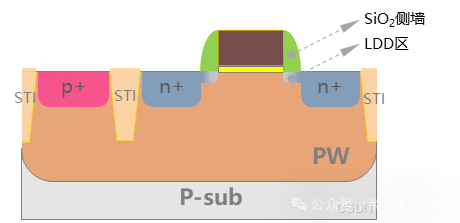

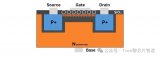

柵極(Gate)是晶體管的核心控制結(jié)構(gòu)��,位于源極(Source)和漏極(Drain)之間���。其功能類似....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 17:33

?1237次閱讀

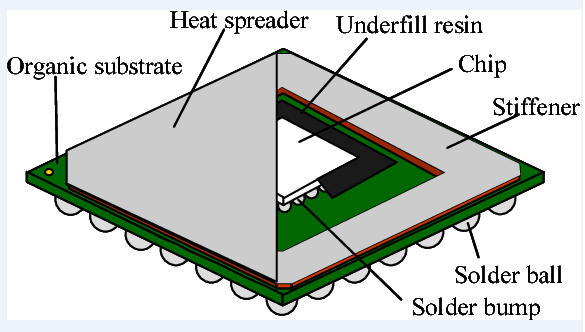

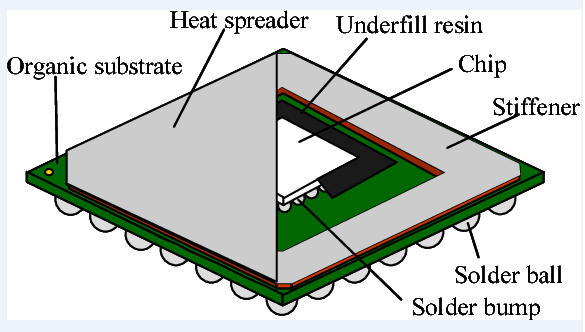

封裝基板設(shè)計是集成電路封裝工程中的核心步驟之一��,涉及將芯片與外部電路連接的基板(substrate)....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 17:30

?861次閱讀

本文介紹了在集成電路制造工藝中的High-K材料的特點���、重要性、優(yōu)勢����,以及工藝流程和面臨的挑戰(zhàn)。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 17:00

?1185次閱讀

本文概述了集成電路制造中的劃片工藝�����,介紹了劃片工藝的種類�����、步驟和面臨的挑戰(zhàn)�����。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 16:57

?1626次閱讀

此處以增強型PMOS��,NMOS為例,通常說的MOS管說的都是增強型MOS管��。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 15:31

?2117次閱讀

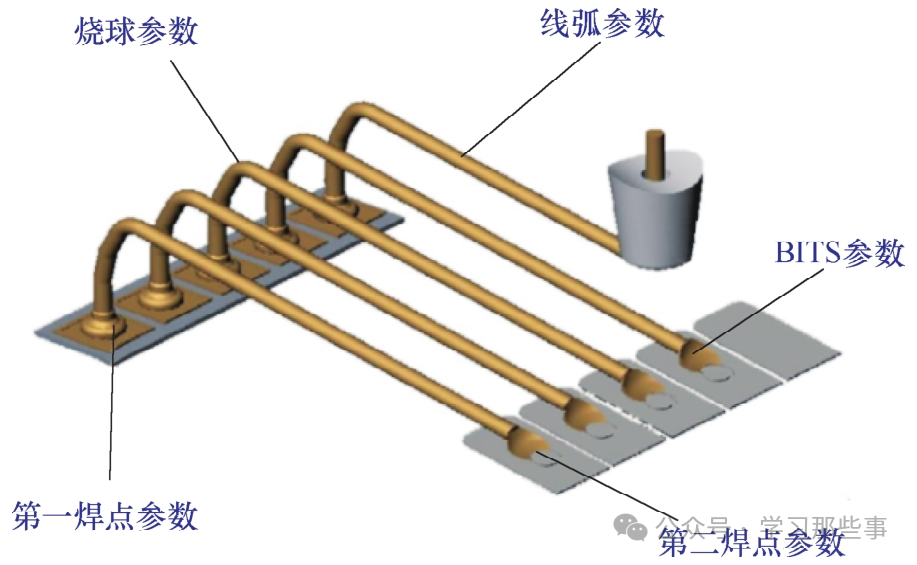

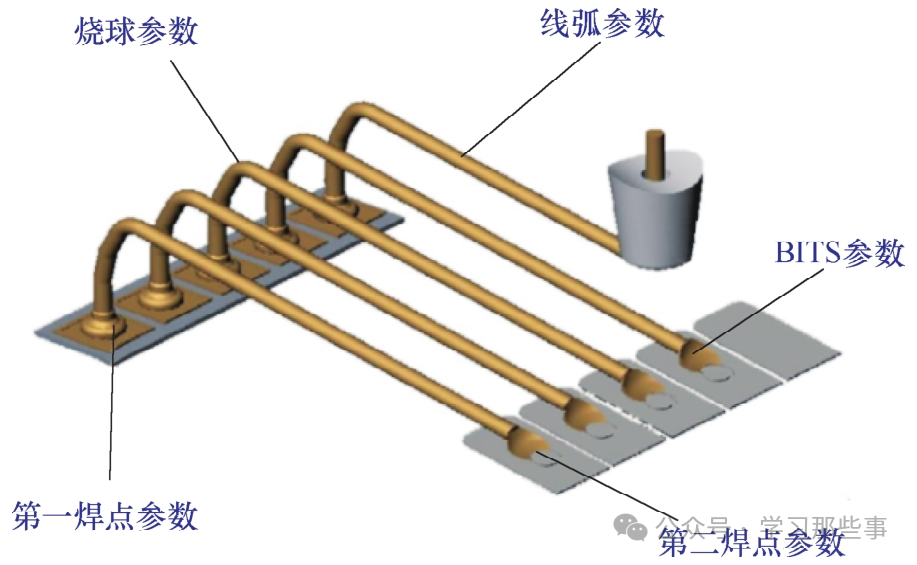

金絲鍵合主要依靠熱超聲鍵合技術(shù)來達成���。熱超聲鍵合融合了熱壓鍵合與超聲鍵合兩者的長處�。通常情況下,熱壓....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 15:28

?1634次閱讀

本文介紹了硅的導熱系數(shù)的特性與影響導熱系數(shù)的因素����。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 15:27

?1339次閱讀

本文介紹了集成電路和光子集成技術(shù)的發(fā)展歷程����,并詳細介紹了鈮酸鋰光子集成技術(shù)和硅和鈮酸鋰復合薄膜技術(shù)。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 15:21

?843次閱讀

本文介紹了集成電路設(shè)計中Standard Cell(標準單元)的概念、作用�����、優(yōu)勢和設(shè)計方法等�。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 15:19

?692次閱讀

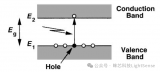

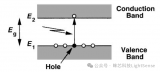

本文介紹了光通信中的光電二極管的工作原理,及其響應度和效率的概念。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 14:27

?934次閱讀

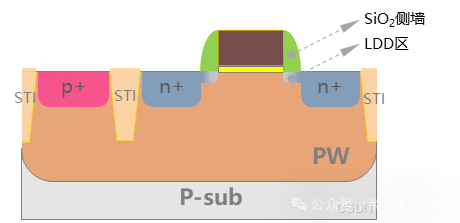

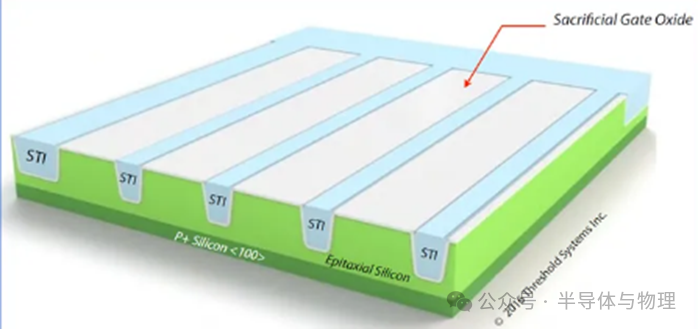

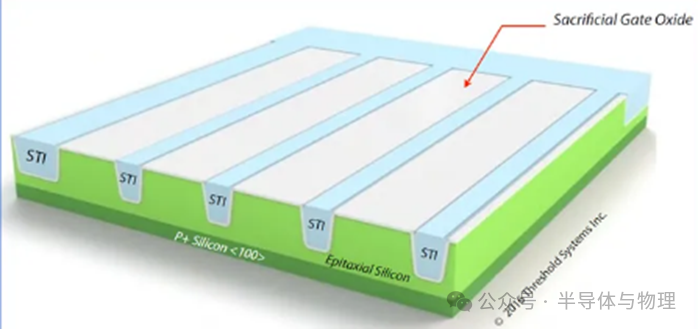

隨著集成電路尺寸縮小至亞微米技術(shù)節(jié)點�����,原始的本征氧化隔離技術(shù)(LocOS)已不適應����。“隔離”是指利用....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-12 14:05

?1367次閱讀

Bump Pattern Design(焊點圖案設(shè)計) 是集成電路封裝設(shè)計中的關(guān)鍵部分��,尤其在BGA....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-06 16:44

?926次閱讀

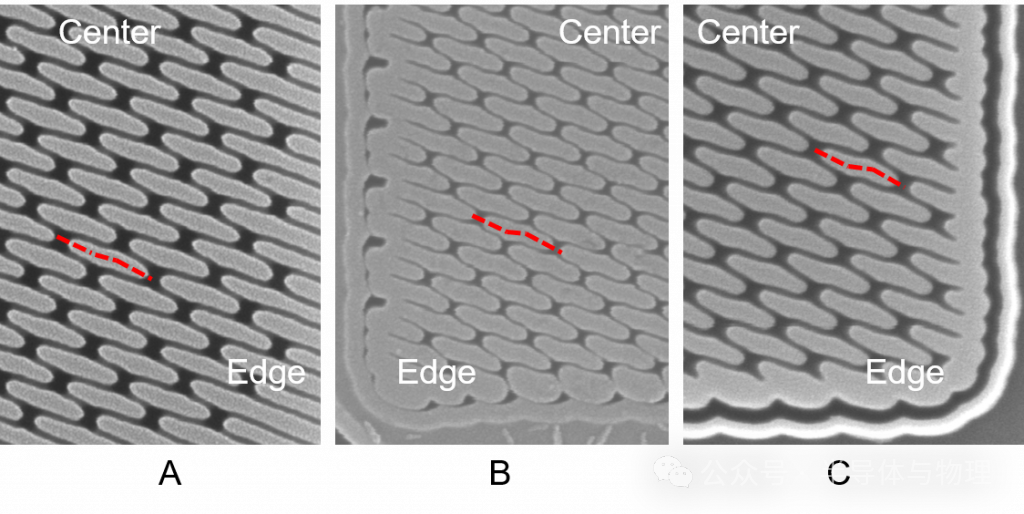

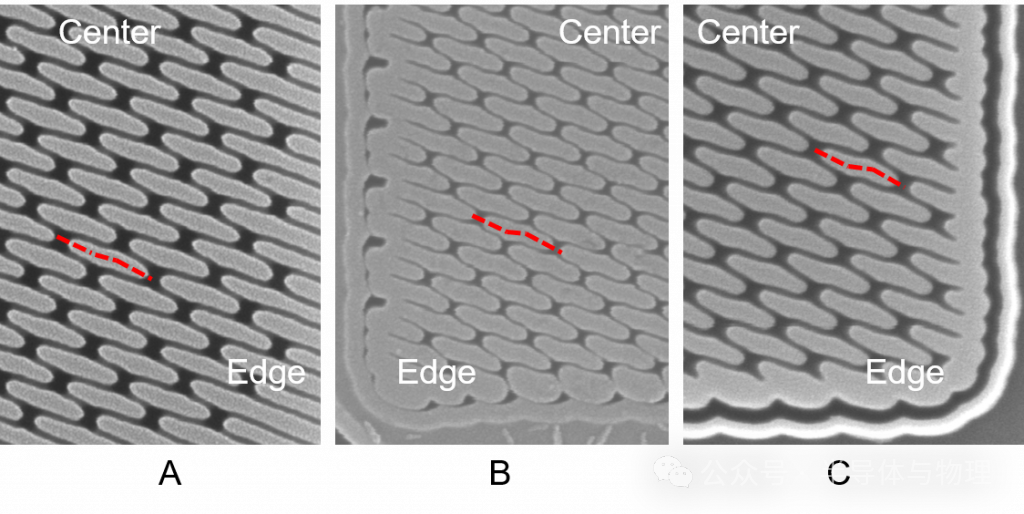

在關(guān)鍵尺寸的在線量測環(huán)節(jié)����,所運用的設(shè)備主要涵蓋 CD-SEM 以及 OCD(optical crit....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-06 16:42

?2182次閱讀

封裝設(shè)計是集成電路(IC)生產(chǎn)過程中至關(guān)重要的一環(huán),它決定了芯片的功能性��、可靠性和制造工藝����。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-06 09:21

?600次閱讀

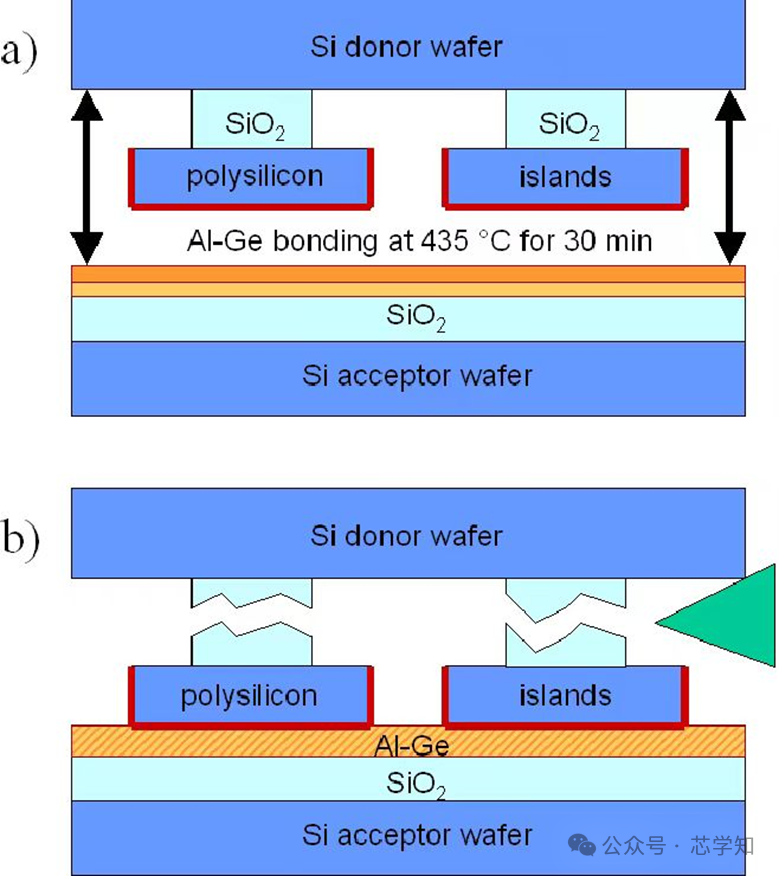

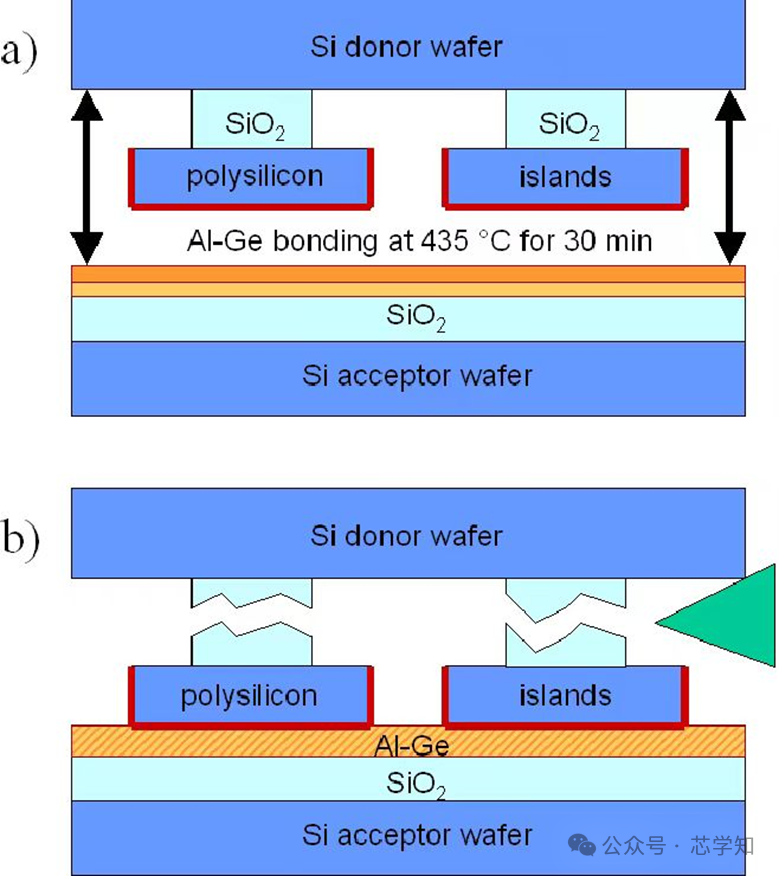

鍵合技術(shù)主要分為直接鍵合和帶有中間層的鍵合。直接鍵合如硅硅鍵合�,陽極鍵合等鍵合條件高,如高溫�、高壓等....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 17:10

?1199次閱讀

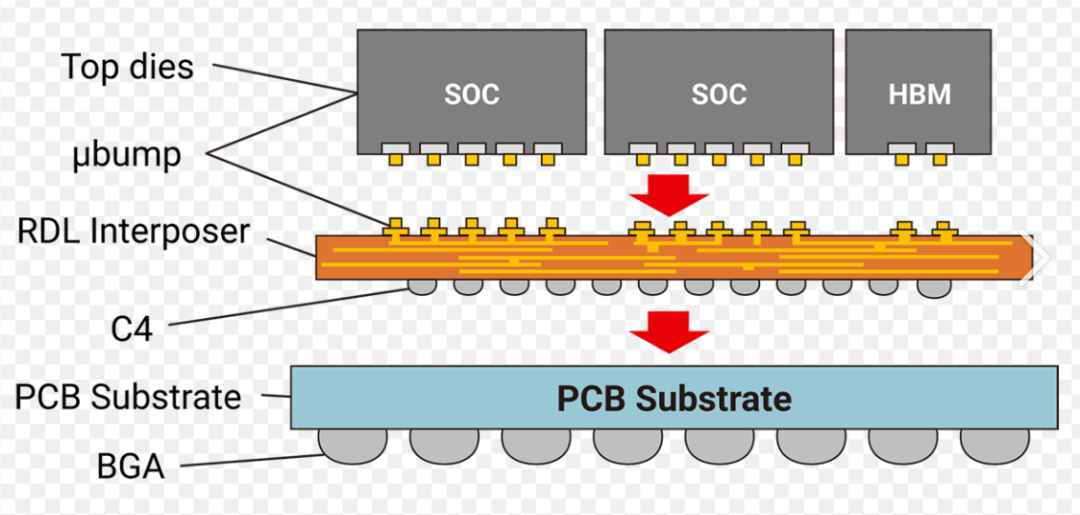

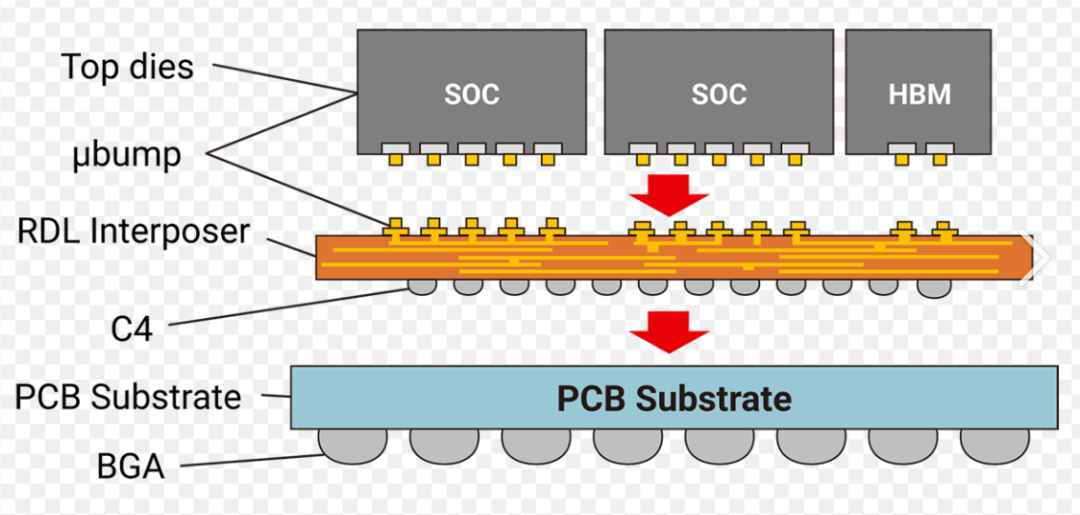

封裝中的RDL(Redistribution Layer,重分布層)是集成電路封裝設(shè)計中的一個重要層....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 17:08

?2179次閱讀

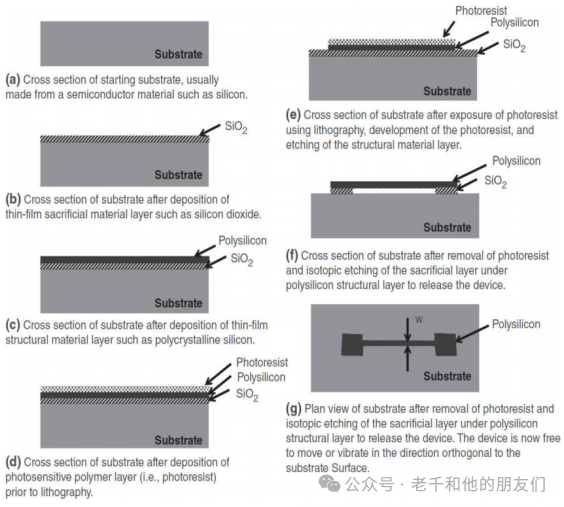

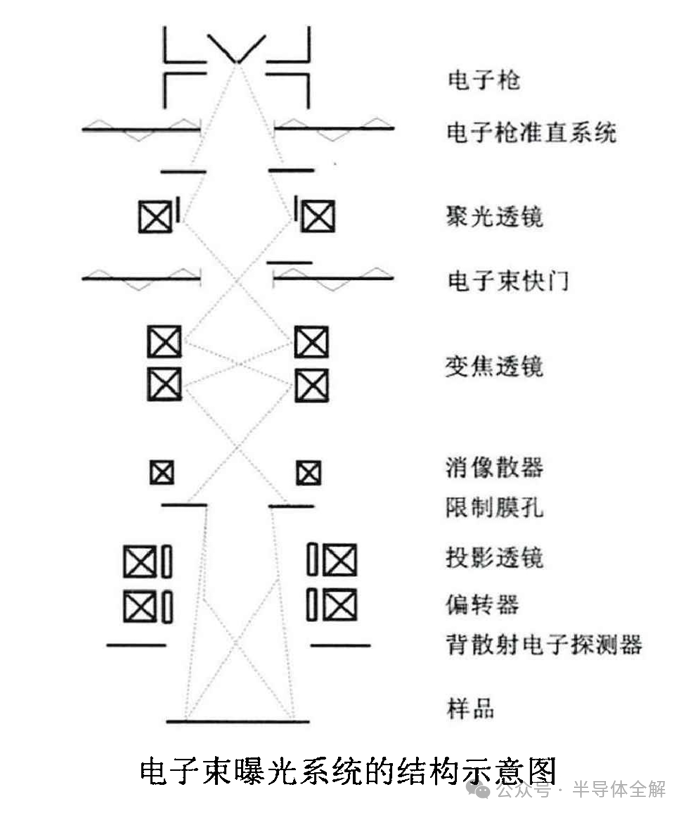

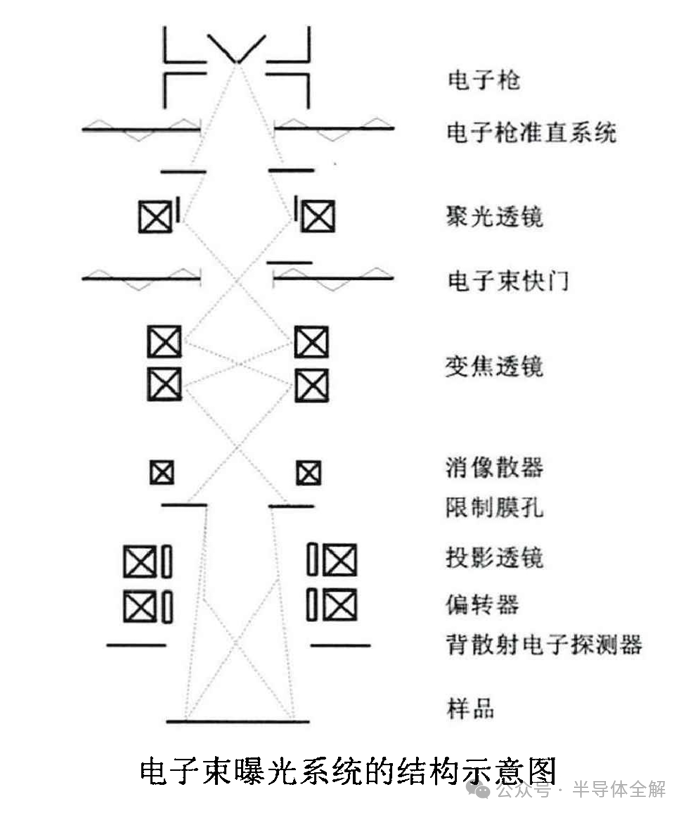

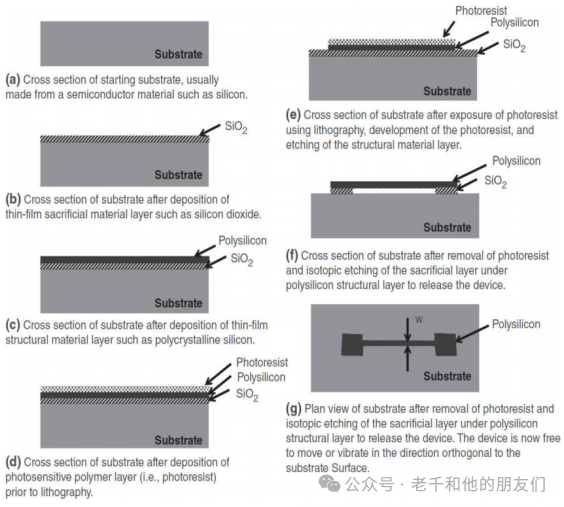

光刻是廣泛應用的芯片加工技術(shù)之一,下圖是常見的半導體加工工藝流程���。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 17:07

?977次閱讀

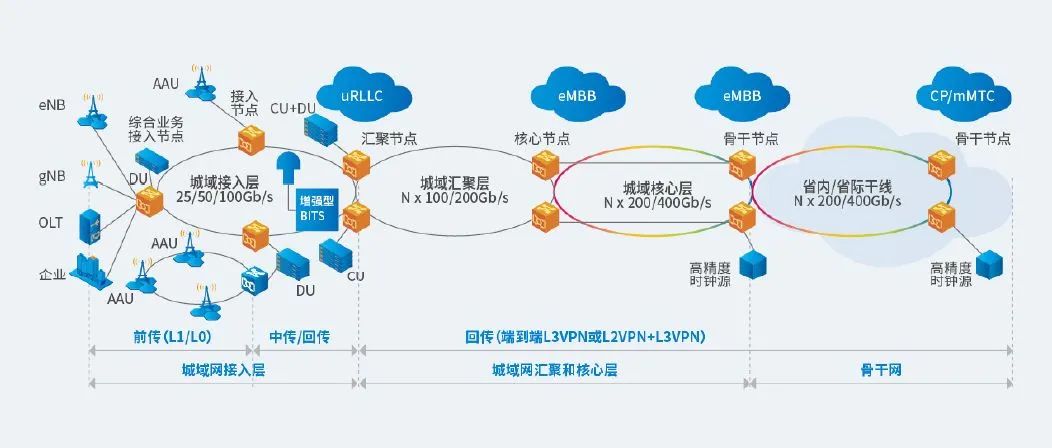

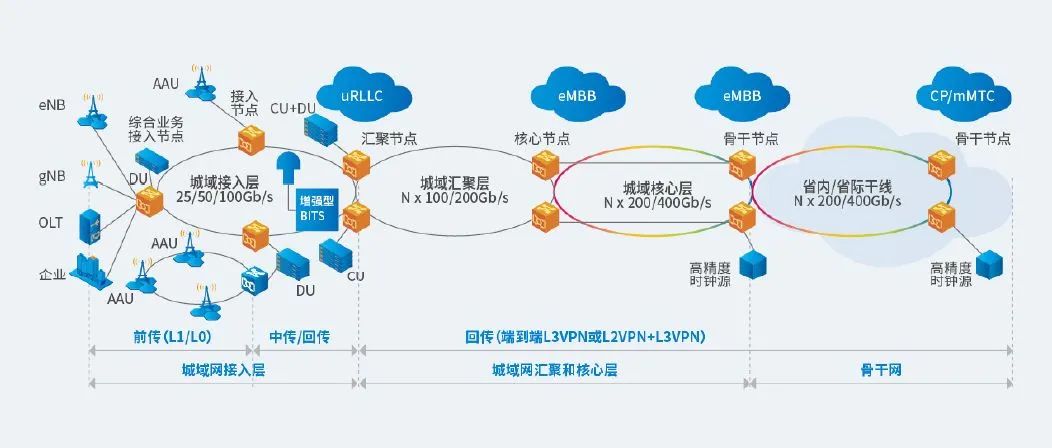

當前光纖系統(tǒng)已廣泛應用于從接入到核心骨干網(wǎng)的各個層級��。各層級因功能需求差異采用不同技術(shù)方案:例如核心....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 11:17

?936次閱讀

在芯片制造中���,有源區(qū)(Active Area)是晶體管的核心工作區(qū)域��,負責電流的導通與信號處理�。它如....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 09:49

?1405次閱讀

封裝設(shè)計Design Rule 是在集成電路封裝設(shè)計中���,為了保證電氣、機械��、熱管理等各方面性能而制定....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 09:45

?463次閱讀

納米技術(shù)是一個高度跨學科的領(lǐng)域�����,涉及在納米尺度上精確控制和操縱物質(zhì)���。集成電路(IC)作為已經(jīng)達到納米....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 09:43

?1826次閱讀

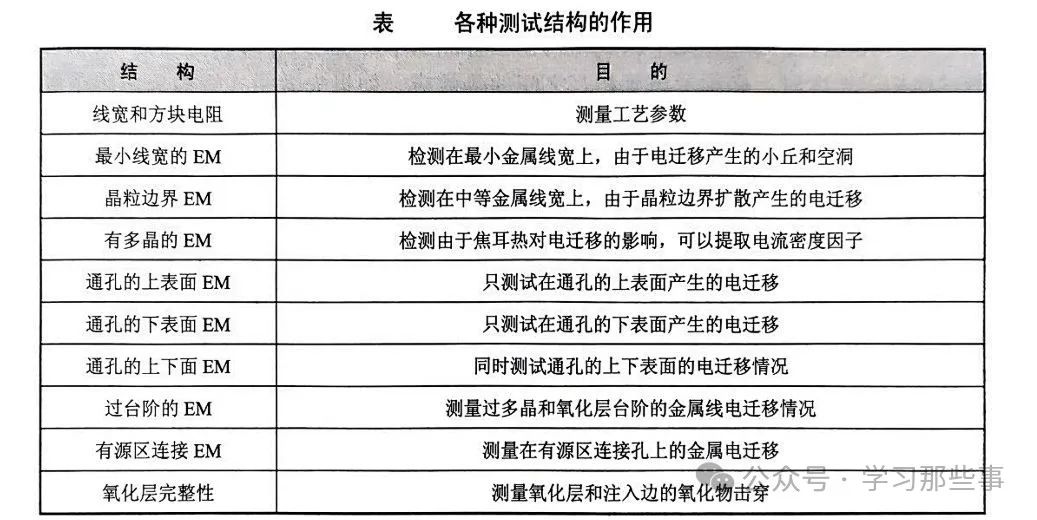

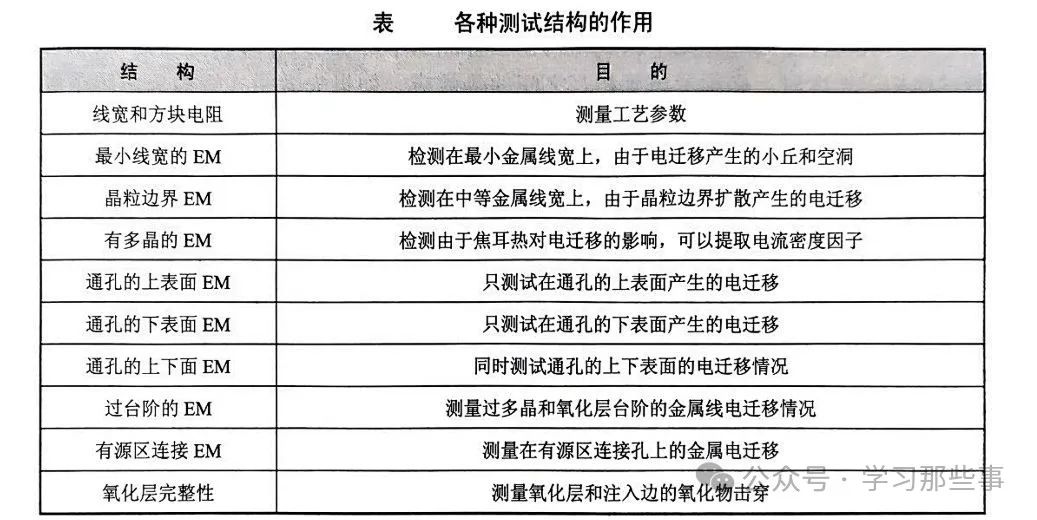

半導體集成電路的可靠性評價是一個綜合性的過程��,涉及多個關(guān)鍵技術(shù)和層面,本文分述如下:可靠性評價技術(shù)概....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-04 09:17

?552次閱讀

如果將芯片封裝比作“房屋結(jié)構(gòu)”����,那么熱仿真就像在建造前做“房屋通風模擬”。在圖紙階段先預測各房間是否....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-03 11:33

?478次閱讀

淺溝道隔離(STI)是芯片制造中的關(guān)鍵工藝技術(shù)����,用于在半導體器件中形成電學隔離區(qū)域,防止相鄰晶體管之....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-03 10:00

?1650次閱讀

一個復雜的處理器可能包含數(shù)億甚至數(shù)十(百)億個晶體管�,這些晶體管通過細金屬線彼此互聯(lián)。芯片的制造過程....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-03 09:56

?1856次閱讀

硅作為半導體材料在集成電路應用中的核心地位無可爭議���,然而��,隨著科技的進步和器件特征尺寸的不斷縮小����,硅....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-03 09:21

?540次閱讀

芯片架構(gòu)設(shè)計的目標是達到功能��、性能��、功耗����、面積(FPA)的平衡。好的芯片架構(gòu)能有效提升系統(tǒng)的整體性能....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-01 16:23

?635次閱讀

隨著集成電路特征尺寸的縮小���,工藝窗口變小�,可靠性成為更難兼顧的因素,設(shè)計上的改善對于優(yōu)化可靠性至關(guān)重....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-01 15:58

?806次閱讀

本文介紹了集成電路開發(fā)中的器件調(diào)試環(huán)節(jié)���,包括其核心目標���、關(guān)鍵技術(shù)與流程等內(nèi)容。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 03-01 14:29

?438次閱讀