今天給大俠帶來(lái)的是一周掌握FPGA Verilog HDL 語(yǔ)法�,今天開(kāi)啟第一天���,下面咱們廢話就不多說(shuō)了�,一起來(lái)看看吧�����。

2022-07-18 09:47:40 2074

2074 FPGA-Verilog HDL語(yǔ)法參考語(yǔ)法規(guī)范下列規(guī)范應(yīng)用于語(yǔ)法描述,規(guī)則采用巴科斯—諾爾范式(B N F)書(shū)寫(xiě):1) 語(yǔ)法規(guī)則按自左向右非終結(jié)字符的字母序組織����。2) 保留字、操作符和標(biāo)點(diǎn)標(biāo)記

2012-08-11 10:33:08

FPGA入門(mén):Verilog/VHDL語(yǔ)法學(xué)習(xí)的經(jīng)驗(yàn)之談 本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA/CPLD邊練邊學(xué)——快速入門(mén)Verilog/VHDL》書(shū)中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤(pán):http

2015-01-29 09:20:41

和Verilog���。VHDL發(fā)展較早�����,語(yǔ)法嚴(yán)謹(jǐn)����;Verilog類似C語(yǔ)言���,語(yǔ)法風(fēng)格比較自由�����。IP核調(diào)用通常也是基于代碼設(shè)計(jì)輸入的基礎(chǔ)之上�,今天很多EDA工具的供應(yīng)商都在打FPGA的如意算盤(pán)�����,FPGA的設(shè)計(jì)也在朝

2015-06-10 12:39:57

Verilog HDL語(yǔ)法,要的拿

2016-01-24 22:53:48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174 Verilog HDL 基本語(yǔ)法

2017-12-08 14:39:50

的具體控制和運(yùn)行��。Verilog HDL語(yǔ)言不僅定義了語(yǔ)法���,而且對(duì)每個(gè)語(yǔ)法結(jié)構(gòu)都定義了清晰的模擬�����、仿真語(yǔ)義。因此�,用這種語(yǔ)言編寫(xiě)的模型能夠使用 Ve r i l o g仿真器進(jìn)行驗(yàn)證。語(yǔ)言從C編程語(yǔ)言

2020-11-30 19:03:38

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語(yǔ)言��。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型�。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)構(gòu)描述

2019-09-06 09:14:16

Verilog HDL的基本語(yǔ)法 .pdf

2012-08-15 15:06:11

本合集資料包括:1.Verilog HDL程序設(shè)計(jì)實(shí)例詳解2.Verilog HDL經(jīng)典教程3.Verilog HDL實(shí)驗(yàn)練習(xí)與語(yǔ)法手冊(cè)4.Verilog HDL硬件描述語(yǔ)言

2020-08-21 10:06:20

verilog HDL語(yǔ)法總結(jié)

2020-03-16 14:26:27

深入理解Android

2012-08-20 15:30:08

本帖最后由 lee_st 于 2018-2-26 00:21 編輯

深入理解Android:WiFi模塊 NFC和GPS卷

2018-02-25 22:26:16

這里有三個(gè)對(duì)深入理解C語(yǔ)言的資料����,覺(jué)得不錯(cuò),分享一下

2014-08-07 21:37:55

深入理解Linux內(nèi)核 中文版+英文原版 經(jīng)典之作

2016-05-17 08:18:47

深入理解SD卡原理和其內(nèi)部結(jié)構(gòu)總結(jié)

2012-08-18 11:11:00

時(shí)鐘系統(tǒng)是處理器的核心�,所以在學(xué)習(xí)STM32所有外設(shè)之前,認(rèn)真學(xué)習(xí)時(shí)鐘系統(tǒng)是必要的,有助于深入理解STM32�����。下面是從網(wǎng)上找的一個(gè)STM32時(shí)鐘框圖,比《STM32中文參考手冊(cè)》里面的是中途看起來(lái)清晰一些:重要的時(shí)鐘:PLLCLK,SYSCLK,HCKL,PCLK1,...

2021-08-12 07:46:20

深入理解LTE-A

2019-02-26 10:21:51

和trcohili的帖子�。深入理解和實(shí)現(xiàn)RTOS_連載1_RTOS的前生今世今天發(fā)布的是第一篇,"RTOS的前生今世"���。通過(guò)軟件系統(tǒng)結(jié)構(gòu)的比對(duì)簡(jiǎn)要的介紹rtos為何而生����。如果讀者對(duì)RTOS

2014-05-29 11:20:54

和trcohili的帖子����。trochili rtos完全是作者興趣所在,且行且堅(jiān)持��,比沒(méi)有duo�。深入理解和實(shí)現(xiàn)RTOS_連載1_RTOS的前生今世今天發(fā)布的是第一篇,"RTOS的前生今世"

2014-05-30 01:02:26

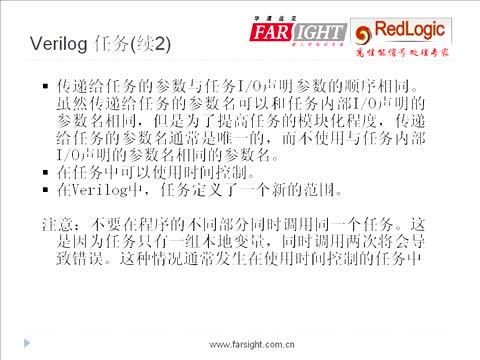

��、視頻)第4講:Verilog HDL語(yǔ)法一:常用語(yǔ)句(視頻)第5講:Verilog HDL語(yǔ)法二:任務(wù)與函數(shù)(視頻)第6講:Verilog HDL語(yǔ)法三:有限狀態(tài)機(jī) (視頻)第7講:QuartusII

2009-03-26 16:37:40

:從零開(kāi)始設(shè)計(jì)FPGA最小系統(tǒng)一: 核心電路(PDF���、視頻)第3講:從零開(kāi)始設(shè)計(jì)FPGA最小系統(tǒng)二: 外圍電路(PDF��、視頻)第4講:Verilog HDL語(yǔ)法一:常用語(yǔ)句(視頻)第5講

2009-03-09 22:56:25

本帖最后由 eehome 于 2013-1-5 09:56 編輯

《Verilog HDL實(shí)驗(yàn)練習(xí)與語(yǔ)法手冊(cè)》-夏宇聞

2012-08-09 14:09:08

博主最近剛開(kāi)始學(xué)習(xí)FPGA設(shè)計(jì)����,選用的開(kāi)發(fā)語(yǔ)言是目前比較流行的Verilog,教材選用的是北京航空航天大學(xué)出版的《夏宇聞Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)教程》(第四版)��,這本書(shū)也是比較經(jīng)典的一本

2022-03-22 10:26:00

《深入理解LINUX內(nèi)存管理》學(xué)習(xí)筆記1

2016-11-07 10:20:16

《深入理解Linux網(wǎng)絡(luò)技術(shù)內(nèi)幕》(EN)

2018-02-06 15:17:30

Verilog HDL 的特點(diǎn)Verilog HDL 語(yǔ)言不僅定義了語(yǔ)法���,而且對(duì)每個(gè)語(yǔ)法結(jié)構(gòu)都定義了清晰的模擬���、仿真語(yǔ)義。使用這種語(yǔ)言編寫(xiě)的模型可以方便地使用 Verilog 仿真器進(jìn)行驗(yàn)證

2018-09-18 09:33:31

行Verilog HDL建模��。FPGA軟件無(wú)線電開(kāi)發(fā)(全階視頻教程+開(kāi)發(fā)板+實(shí)例)詳情鏈接:http://url.elecfans.com/u/5e4a12f2ba手把手教你設(shè)計(jì)人工智能芯片及系統(tǒng)(全階

2019-11-26 11:27:34

[導(dǎo)讀] 從這篇文章開(kāi)始���,將會(huì)不定期更新關(guān)于嵌入式C語(yǔ)言編程相關(guān)的個(gè)人認(rèn)為比較重要的知識(shí)點(diǎn),或者踩過(guò)的坑�����。為什么要深入理解棧�?做C語(yǔ)言開(kāi)發(fā)如果棧設(shè)置不合理或者使用不對(duì),棧就會(huì)溢出���,溢出就會(huì)遇到無(wú)法

2022-02-15 06:09:14

句11.Verilog HDL語(yǔ)言實(shí)現(xiàn)組合邏輯電路12.Verilog HDL語(yǔ)言實(shí)現(xiàn)時(shí)序邏輯電路第三階段 雖然利用第二階段課程學(xué)到的HDL基本語(yǔ)法可以完成大部分的FPGA功能���,但相對(duì)復(fù)雜的FPGA系統(tǒng)設(shè)計(jì)中

2018-09-19 11:34:03

���,用它可以表示邏輯電路圖、邏輯表達(dá)式����,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語(yǔ)言�,都是在20世紀(jì)80年代中期開(kāi)發(fā)出來(lái)的。記得在剛接觸FPGA

2016-03-16 10:45:02

的是VHDL和Verilog�����。VHDL發(fā)展較早��,語(yǔ)法嚴(yán)謹(jǐn)���;Verilog類似C語(yǔ)言����,語(yǔ)法風(fēng)格比較自由��。IP核調(diào)用通常也是基于代碼設(shè)計(jì)輸入的基礎(chǔ)之上,今天很多EDA工具的供應(yīng)商都在打FPGA的如

2017-12-04 21:11:46

1331293596第三階段雖然利用第二階段課程學(xué)到的HDL基本語(yǔ)法可以完成大部分的FPGA功能��,但相對(duì)復(fù)雜的FPGA系統(tǒng)設(shè)計(jì)中��,如果能夠合理的應(yīng)用Verilog HDL的高級(jí)語(yǔ)法結(jié)構(gòu)��,可以達(dá)到事半功倍的效果

2015-10-27 17:57:38

深入理解ES6之函數(shù)

2020-05-22 07:40:56

二極管鉗位作用如何運(yùn)用?在電路設(shè)計(jì)過(guò)程中很多位置需要用二極管鉗位�����,如何深入理解和運(yùn)用�?

2019-04-03 03:03:34

如何更加深入理解MOSFET開(kāi)關(guān)損耗�����?Coss產(chǎn)生開(kāi)關(guān)損耗與對(duì)開(kāi)關(guān)過(guò)程有什么影響��?

2021-04-07 06:01:07

為什么要深入理解棧����?做C語(yǔ)言開(kāi)發(fā)如果棧設(shè)置不合理或者使用不對(duì),棧就會(huì)溢出�,溢出就會(huì)遇到無(wú)法預(yù)測(cè)亂飛現(xiàn)象。所以對(duì)棧的深入理解是非常重要的����。注:動(dòng)畫(huà)如果看不清楚可以電腦看更清晰啥是棧先來(lái)看一段動(dòng)畫(huà):沒(méi)有

2022-02-15 07:01:00

://www.kx-soc.com/)編著,是初學(xué)Verilog理論不錯(cuò)的好書(shū)�����。(2)《深入淺出玩轉(zhuǎn)FPGA》吳厚航北京航空航天大學(xué)出版工程師項(xiàng)目實(shí)戰(zhàn)演習(xí)的案例分析����,更具實(shí)踐價(jià)值。(3)《Verilog 數(shù)字系統(tǒng)設(shè)計(jì)教程》夏宇聞

2012-02-03 11:11:35

本帖最后由 eehome 于 2013-1-5 10:01 編輯

EDA先鋒工作室的精品書(shū)籍��,國(guó)內(nèi)少有的系統(tǒng)講述FPGA設(shè)計(jì)和驗(yàn)證的好書(shū)�,特別是驗(yàn)證部分很精華,現(xiàn)在和大家分享��,同時(shí)附上本書(shū)的實(shí)例源代碼和Verilog HDL語(yǔ)法國(guó)際標(biāo)準(zhǔn)��。

2011-08-02 14:54:41

This manual describes the Verilog portion of Synopsys FPGACompiler II / FPGA Express application

2009-07-23 10:01:29 79

79 采用 Verilog HDL 語(yǔ)言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語(yǔ)言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 Verilog-HDL實(shí)踐與應(yīng)用系統(tǒng)設(shè)計(jì)本書(shū)從實(shí)用的角度介紹了硬件描述語(yǔ)言Verilog-HDL�。通過(guò)動(dòng)手實(shí)踐,體驗(yàn)Verilog-HDL的語(yǔ)法結(jié)構(gòu)、功能等內(nèi)涵。在前五章,以簡(jiǎn)單的實(shí)例列舉了Verilog-HDL的用法;

2009-11-14 22:57:40 146

146 什么是Verilog HDL����?

Verilog HDL是一種硬件描述語(yǔ)言���,用于從算法級(jí)���、門(mén)級(jí)到開(kāi)關(guān)級(jí)的多種抽象設(shè)計(jì)層次的數(shù)字系統(tǒng)建模。被建模的數(shù)字系統(tǒng)

2009-01-18 14:53:26 3678

3678

摘 要:通過(guò)設(shè)計(jì)實(shí)例詳細(xì)介紹了用Verilog HDL語(yǔ)言開(kāi)發(fā)FPGA/CPLD的方法����,并通過(guò)與其他各種輸入方式的比較,顯示出使用Verilog HDL語(yǔ)言的優(yōu)越性��。

2009-06-20 11:51:28 1857

1857

Verilog HDL語(yǔ)言簡(jiǎn)介

1.什么是Verilog HDLVerilog HDL是硬件描述語(yǔ)言的一種��,用于數(shù)

2010-02-09 08:59:33 3609

3609 Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優(yōu)點(diǎn):類似C語(yǔ)言���,上手容易��,靈活。大小寫(xiě)敏感。在寫(xiě)激勵(lì)和建模方面有優(yōu)勢(shì)����。

2011-01-11 10:45:29 1182

1182 在我國(guó)使用Verilog HDL的公司比使用VHDL的公司多。從EDA技術(shù)的發(fā)展上看�����,已出現(xiàn)用于CPLD/FPGA設(shè)計(jì)的硬件C語(yǔ)言編譯軟件����,雖然還不成熟,應(yīng)用極少��,但它有可能會(huì)成為繼VHDL和Verilog之后���,設(shè)計(jì)大規(guī)模CPLD/FPGA的又一種手段����。

2011-03-12 11:21:20 1686

1686 《Verilog HDL 程序設(shè)計(jì)教程》對(duì)Verilog HDL程序設(shè)計(jì)作了系統(tǒng)全面的介紹�����,以可綜合的設(shè)計(jì)為重點(diǎn)�����,同時(shí)對(duì)仿真和模擬也作了深入的闡述?!?b class="flag-6" style="color: red">Verilog HDL 程序設(shè)計(jì)教程》以Verilog-1995標(biāo)準(zhǔn)為基礎(chǔ)

2011-09-22 15:53:36 0

0 Verilog_HDL的基本語(yǔ)法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型����。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)

2012-10-08 14:48:31 0

0 本書(shū)以實(shí)例講解的方式對(duì)HDL語(yǔ)言的設(shè)計(jì)方法進(jìn)行介紹。全書(shū)共分9章�,第1章至第3章主要介紹了Verilog HDL語(yǔ)言的基本概念、設(shè)計(jì)流程���、語(yǔ)法及建模方式等��。

2012-11-28 13:32:57 943

943 電子發(fā)燒友網(wǎng)站提供《深入理解LINUX內(nèi)核(中文版)_ 陳莉君/馮銳/牛欣源譯.txt》資料免費(fèi)下載

2015-02-11 11:16:33 0

0 Verilog HDL程序設(shè)計(jì)與實(shí)踐著重介紹了Verilog HDL語(yǔ)言

2015-10-29 14:45:47 21

21 掌握基本語(yǔ)法�,還能夠獲得深層次理解���。從結(jié)構(gòu)上講��,本書(shū)以Verilog HDL的各方面開(kāi)發(fā)為主線�����,遵照硬件應(yīng)用系統(tǒng)開(kāi)發(fā)的基本步驟和思路進(jìn)行詳細(xì)講解�����,并穿插介紹ISE開(kāi)發(fā)工具的操作技巧與注意事項(xiàng)�,具備很強(qiáng)的可

2015-12-31 15:56:36 7

7 深入理解三極管的相應(yīng)資料����,有需要的可以下載,不喜勿噴

2016-01-14 16:19:11 24

24 Verilog HDL實(shí)驗(yàn)練習(xí)與語(yǔ)法手冊(cè)-高教

2016-05-11 11:30:19 0

0 Verilog_HDL語(yǔ)言的學(xué)習(xí)���,為FPGA編程打下堅(jiān)實(shí)的基礎(chǔ)

2016-05-19 16:40:52 12

12 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí)����,目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法��,初步了解并掌握Verilog HDL語(yǔ)言的基本要素���,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模���。

2016-07-15 15:27:00 0

0 verilog HDL,fpga,硬件電路學(xué)習(xí)資料

2016-09-01 14:55:49 0

0 設(shè)計(jì)與驗(yàn)證�,很不錯(cuò)的一本書(shū),《設(shè)計(jì)與驗(yàn)證》以實(shí)例講解的方式對(duì)HDL語(yǔ)言的設(shè)計(jì)方法進(jìn)行介紹�。全書(shū)共分9章,第1章至第3章主要介紹了Verilog HDL語(yǔ)言的基本概念����、設(shè)計(jì)流程、語(yǔ)法及建模方式等內(nèi)容

2016-10-10 17:04:40 566

566 深入理解Android之資源文件

2017-01-22 21:11:02 22

22 基于FPGA Verilog-HDL語(yǔ)言的串口設(shè)計(jì)

2017-02-16 00:08:59 35

35 《深入理解Android》文前

2017-03-19 11:23:20 0

0 《深入理解Android:卷I》

2017-03-19 11:23:45 0

0 深入理解Android網(wǎng)絡(luò)編程

2017-03-19 11:26:35 1

1 深入理解Linux內(nèi)核(第三版)中文版

2017-11-28 11:54:15 0

0 深入理解C指針

2018-03-21 09:42:45 116

116 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL入門(mén)教程之Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)教程��。

2018-09-20 15:51:26 80

80 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí)�,目的是使初學(xué)者能夠迅速掌握HDL 設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素�,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2019-02-11 08:00:00 95

95 Verilog HDL作為現(xiàn)在最流行的FPGA開(kāi)發(fā)語(yǔ)言����,當(dāng)然是入門(mén)基礎(chǔ)。

2019-02-18 14:47:00 10320

10320 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語(yǔ)言�。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)構(gòu)描述的語(yǔ)言����。

2019-03-08 14:29:12 12094

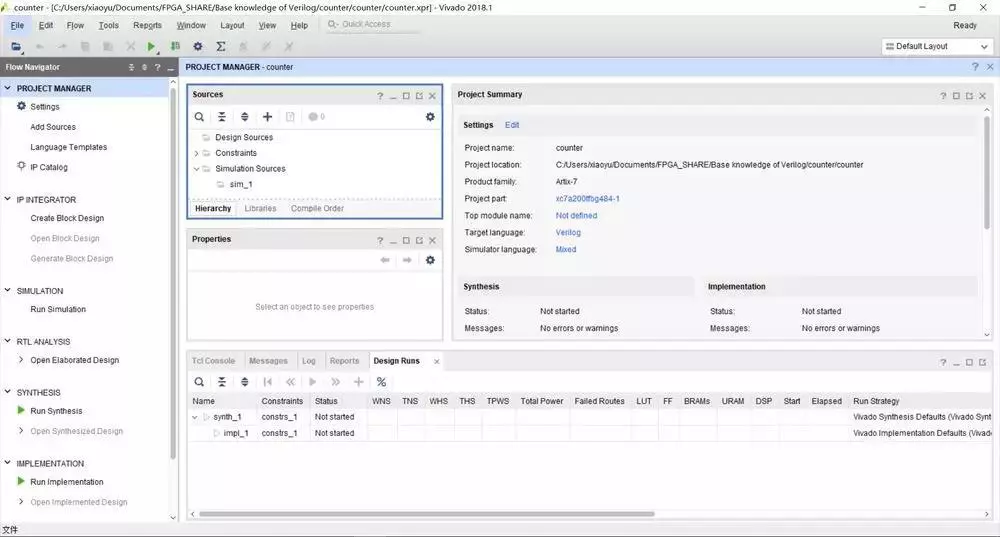

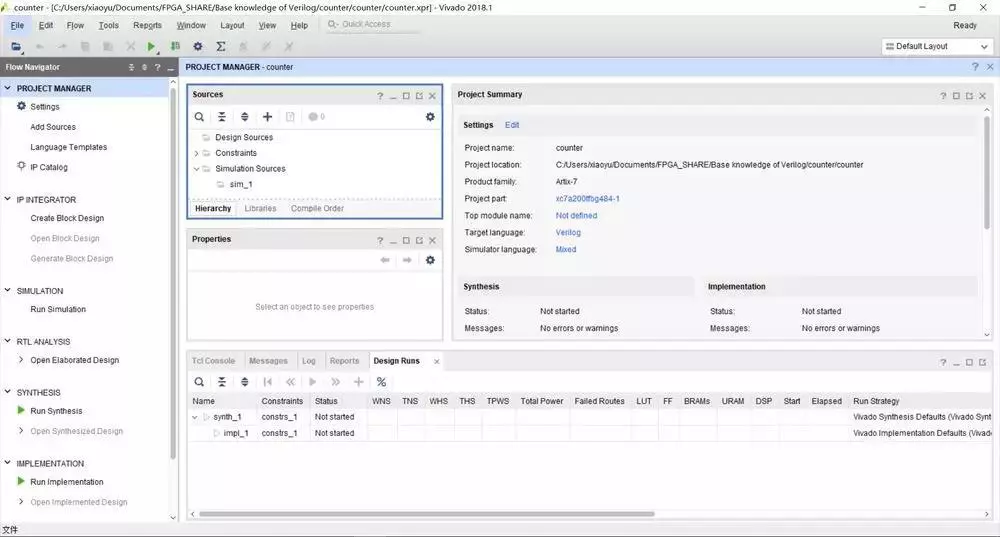

12094 中國(guó)大學(xué)MOOC

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)����、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用����,并循序漸進(jìn)地從組合邏輯���、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始�,深入到FPGA的基礎(chǔ)應(yīng)用�����、綜合應(yīng)用和進(jìn)階應(yīng)用�����。

2019-08-06 06:12:00 3450

3450

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線�,全面講解FPGA的原理及電路設(shè)計(jì)����、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯��、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始�,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用��。

2019-12-02 07:10:00 2914

2914

大家都知道軟件設(shè)計(jì)使用軟件編程語(yǔ)言,例如我們熟知的C���、Java等等�,而FPGA設(shè)計(jì)使用的是HDL語(yǔ)言�����,例如VHDL和Verilog HDL��。說(shuō)的直白點(diǎn)�����,FPGA的設(shè)計(jì)就是邏輯電路的實(shí)現(xiàn)�����,就是把我們

2019-12-05 07:10:00 2977

2977

Verilog HDL是一種硬件描述語(yǔ)言�����,以文本形式來(lái)描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言���,用它可以表示邏輯電路圖��、邏輯表達(dá)式�����,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能����。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語(yǔ)言,都是在20世紀(jì)80年代中期開(kāi)發(fā)出來(lái)的��。

2019-11-13 07:03:00 3029

3029 硬件描述語(yǔ)言基本語(yǔ)法和實(shí)踐

(1)VHDL 和Verilog HDL的各自特點(diǎn)和應(yīng)用范圍

(2)Verilog HDL基本結(jié)構(gòu)語(yǔ)言要素與語(yǔ)法規(guī)則

(3) Verilog HDL組合邏輯語(yǔ)句結(jié)構(gòu)

2019-07-03 17:36:00 53

53 老司機(jī)帶你深入理解ST庫(kù)中的assert_param語(yǔ)句

2020-03-14 14:52:50 3373

3373 更加深入理解I2C總線�����、協(xié)議及應(yīng)用

2020-03-20 09:29:21 2999

2999

的是硬件描述語(yǔ)言���。最為流行的硬件描述語(yǔ)言有兩種Verilog HDL/VHDL����,均為IEEE標(biāo)準(zhǔn)����。Verilog HDL具有C語(yǔ)言基礎(chǔ)就很容易上手��,而VHDL語(yǔ)言則需要Ada編程基礎(chǔ)�。另外Verilog

2020-09-01 11:47:09 4002

4002

作者:小魚(yú)�����,Xilinx學(xué)術(shù)合作 一.概述 在文章《Verilog HDL入門(mén)思路梳理》我們說(shuō)過(guò)應(yīng)該如何去學(xué)習(xí)Verilog HDL描述�。然而第一步,我們需要知道Verilog有哪些語(yǔ)法�����,它是否可以

2021-01-02 09:45:00 1280

1280

簡(jiǎn)單介紹Verilog HDL語(yǔ)言和仿真工具��。

2021-05-06 16:17:10 617

617 摘要:Verilog HDL硬件描述語(yǔ)言是在用途最廣泛的C語(yǔ)言的基礎(chǔ)上發(fā)展起來(lái)的一種硬件描述語(yǔ)言�,具有靈活性高、易學(xué)易用等特點(diǎn)�。Verilog HDL可以在較短的時(shí)間內(nèi)學(xué)習(xí)和掌握,FPGA

2021-06-30 15:31:54 2419

2419

深入理解MOS管電子版資源下載

2021-07-09 09:43:01 0

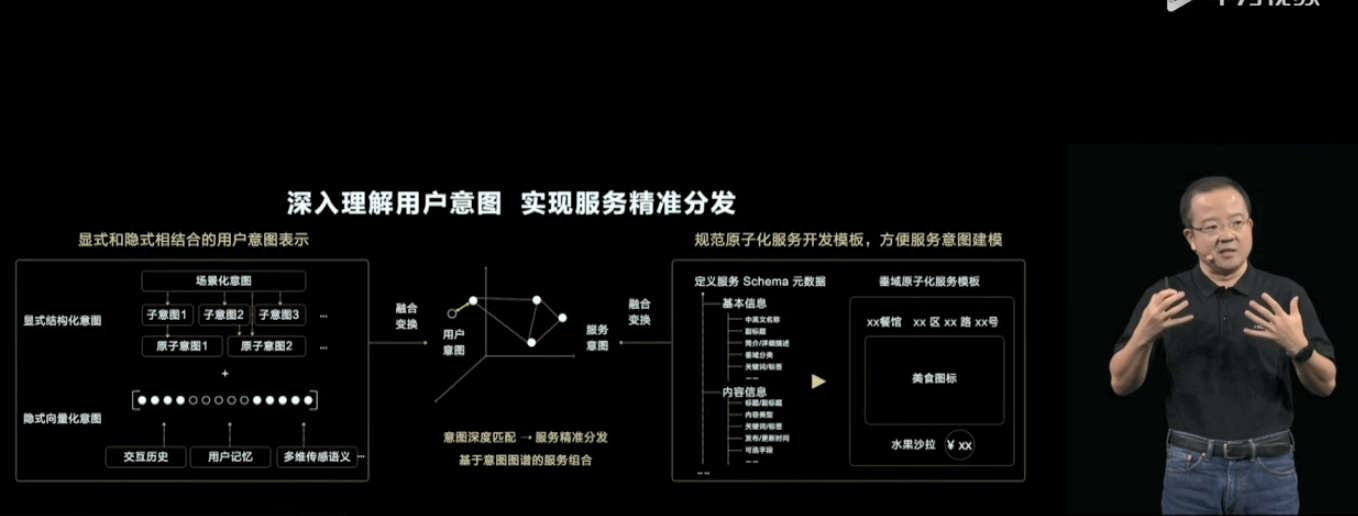

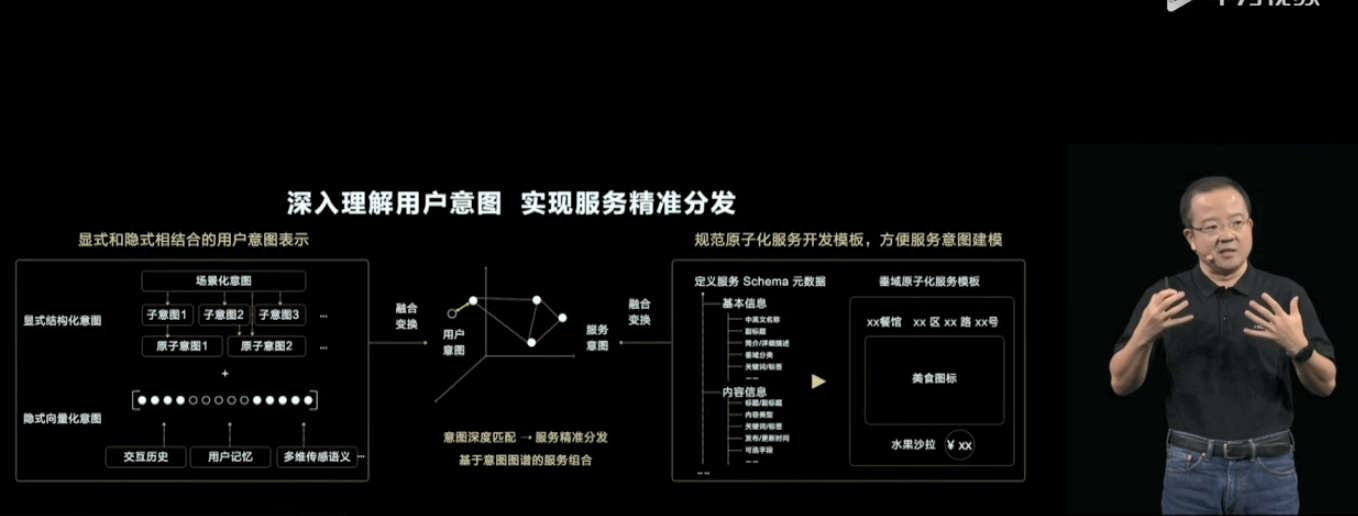

0 如何深入理解用戶意圖��,實(shí)現(xiàn)服務(wù)精準(zhǔn)分發(fā)�。

2021-10-22 15:41:08 1573

1573

深入理解計(jì)算機(jī)系統(tǒng)中文版pdf下載

2021-11-11 18:11:26 0

0 不知道你是否想過(guò)�����,一個(gè)LED燈點(diǎn)亮過(guò)程的本質(zhì)是什么�。當(dāng)你是一個(gè)小白的時(shí)候���,點(diǎn)亮一個(gè)LED燈���,IDE都會(huì)幫你做好所有的事情,你只需要點(diǎn)擊一下編譯即可�����。但是����,當(dāng)你成長(zhǎng)到一定程度時(shí)����,就需要好好想想,一個(gè)LED的點(diǎn)亮����,其實(shí)是對(duì)單片機(jī)中背后原理機(jī)制真正的深入理解。今天我就帶你,來(lái)深入理解一個(gè)LDE點(diǎn)亮的過(guò)程���。

2021-12-22 19:08:21 9

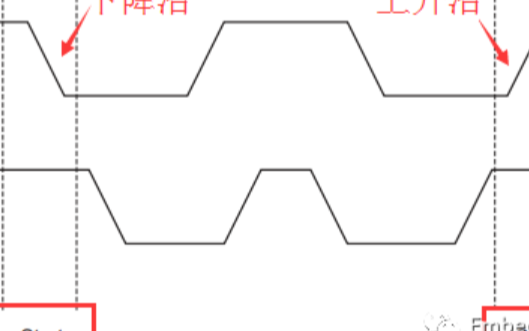

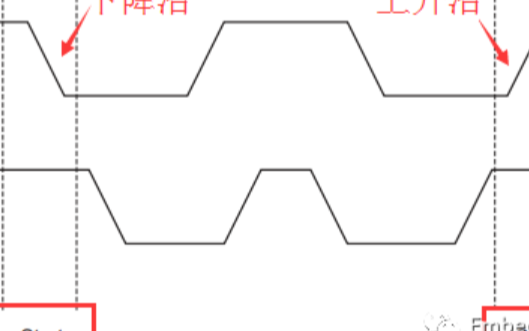

9 (69)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)21.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):時(shí)鐘激勵(lì)25)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2021-12-29 19:42:19 0

0 (77)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)31.1 目錄1)目錄2)FPGA簡(jiǎn)介3)Verilog HDL簡(jiǎn)介4)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)35)結(jié)語(yǔ)1.2 FPGA簡(jiǎn)介FPGA

2021-12-29 19:42:39 0

0 Verilog HDL入門(mén)教程-Verilog HDL的基本語(yǔ)法

2022-01-07 09:23:42 159

159 為什么要深入理解棧���?做C語(yǔ)言開(kāi)發(fā)如果棧設(shè)置不合理或者使用不對(duì),棧就會(huì)溢出���,溢出就會(huì)遇到無(wú)法預(yù)測(cè)亂飛現(xiàn)象��。所以對(duì)棧的深入理解是非常...

2022-01-26 17:55:42 2

2 本文首發(fā)于 GiantPandaCV :深入理解神經(jīng)網(wǎng)絡(luò)中的反(轉(zhuǎn)置)卷積作者:梁德澎本文主要是把之前在知乎上的回答:反卷積和上采樣+卷積的區(qū)別...

2022-02-07 11:17:57 0

0 想深入理解操作系統(tǒng)的進(jìn)程調(diào)度�,需要先獲得一些準(zhǔn)備知識(shí)���,這樣后面就不懵圈啦:

2022-03-16 10:58:03 1952

1952 要想深入理解Verilog就必須正視Verilog語(yǔ)言同時(shí)具備硬件特性和軟件特性���。

2022-07-07 09:54:48 1124

1124 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊��。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)構(gòu)描述的語(yǔ)言�����。

2022-12-08 14:00:57 1928

1928 要想深入理解Verilog就必須正視Verilog語(yǔ)言同時(shí)具備硬件特性和軟件特性�����。在當(dāng)下的教學(xué)過(guò)程中,教師和教材都過(guò)于強(qiáng)調(diào)Verilog語(yǔ)言的硬件特性和可綜合特性��。將Verilog語(yǔ)言的行為級(jí)語(yǔ)法

2023-05-25 15:10:21 642

642

要想深入理解Verilog就必須正視Verilog語(yǔ)言同時(shí)具備硬件特性和軟件特性��。在當(dāng)下的教學(xué)過(guò)程中����,教師和教材都過(guò)于強(qiáng)調(diào)Verilog語(yǔ)言的硬件特性和可綜合特性。將Verilog語(yǔ)言的行為級(jí)語(yǔ)法

2023-05-25 15:10:44 576

576

正在加载...

2074

2074 2074

2074 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論