中國大學(xué)MOOC 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1640文章

21899瀏覽量

611403 -

Xilinx

+關(guān)注

關(guān)注

73文章

2178瀏覽量

123812 -

開發(fā)

+關(guān)注

關(guān)注

0文章

371瀏覽量

41231

發(fā)布評論請先 登錄

相關(guān)推薦

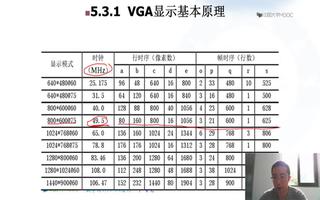

數(shù)字設(shè)計(jì)FPGA應(yīng)用:VGA顯示的基本原理分析

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:時(shí)序邏輯電路FPGA的實(shí)現(xiàn)

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

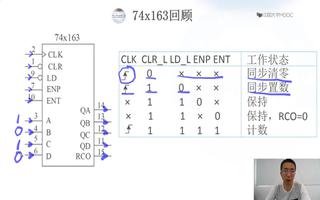

數(shù)字設(shè)計(jì)FPGA應(yīng)用:74x163回顧

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

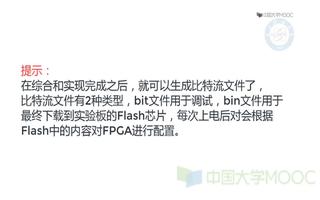

數(shù)字設(shè)計(jì)FPGA應(yīng)用:硬件描述語言與VIVADO

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:FPGA的基本實(shí)踐

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:7系列FPGA及7a35tftg256-1特性

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:按鍵掃描設(shè)計(jì)

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:矩陣式按鍵的設(shè)計(jì)

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:LED流水燈的程序編寫

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:實(shí)現(xiàn)LED小燈功能

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

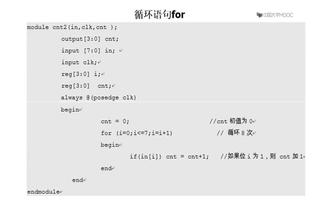

數(shù)字設(shè)計(jì)FPGA應(yīng)用:循環(huán)語句for

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:FPGA的基本邏輯結(jié)構(gòu)

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

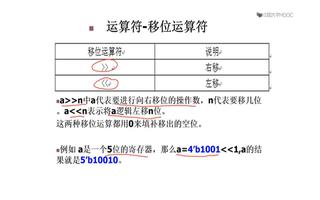

數(shù)字設(shè)計(jì)FPGA應(yīng)用:移位運(yùn)算符

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

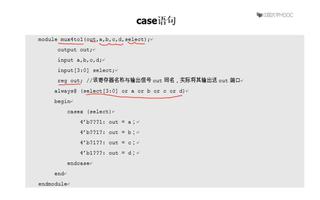

數(shù)字設(shè)計(jì)FPGA應(yīng)用:case語句

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

數(shù)字設(shè)計(jì)FPGA應(yīng)用:Verilog HDL語言基本結(jié)構(gòu)

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始

Verilog HDL語言及VIVADO的應(yīng)用

Verilog HDL語言及VIVADO的應(yīng)用

評論