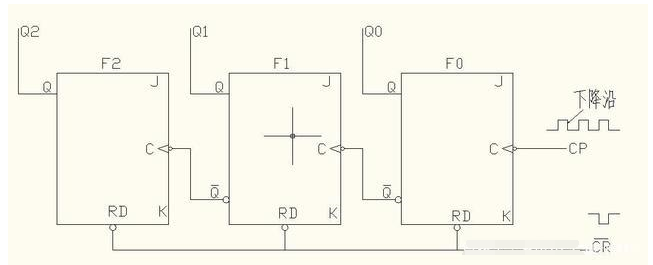

用一個(gè)外加觸發(fā)器使計(jì)數(shù)器可靠的自行復(fù)位

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術(shù)應(yīng)用>電子技術(shù)>電路圖>信號(hào)處理電子電路圖>用一個(gè)外加觸發(fā)器使計(jì)數(shù)器可靠的自行復(fù)位

相關(guān)推薦

19

19 170

170

1317

1317 1435

1435

549

549 297

297

886

886

11617

11617

4676

4676

2

2 264

264 1

1 3

3 0

0 1

1 0

0 1

1 0

0 0

0 3

3 0

0 0

0 1874

1874 1762

1762 511

511 16964

16964

5720

5720

3105

3105

15572

15572 44473

44473

15

15 1630

1630 19

19 11289

11289 91461

91461

12686

12686 15455

15455

6965

6965

0

0 1

1 2315

2315

751

751

23884

23884

14537

14537

17874

17874

23837

23837

14774

14774

2170

2170

62199

62199 93353

93353

27069

27069

84513

84513

23829

23829

67188

67188

40935

40935

15

15 8

8 196

196 3245

3245

963

963

1723

1723

2756

2756

17358

17358

11549

11549 2214

2214

57

57 14012

14012

11724

11724 1763

1763 4276

4276

7879

7879

290

290

評(píng)論