1�、CORDIC 理論

1.1��、 坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī)CORDIC

坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī)CORDIC(COordinate Rotation DIgital Computer)算法���,通過移位和加減運(yùn)算����,能遞歸計(jì)算常用函數(shù)值

2010-07-28 17:57:22 1661

1661 我現(xiàn)在寫著一個(gè)CORDIC 的 verilog 代碼�,但在邏輯上遇到問題。https://www.edaplayground.com/x/3tHk �����, 為何 y[2] == 0 ? -->

2017-05-14 00:32:53

IP CORE CORDIC ALGO EC/ECP CONF

2023-03-30 12:01:20

IP CORE CORDIC ALGO ECP3 CONF

2023-03-30 12:01:21

SITE LICENSE CORDIC ALGO ECP3

2023-03-30 12:02:10

IP CORE CORDIC ALGO ECP2 CONF

2023-03-30 12:01:21

IP CORE CORDIC ALGO XP2 CONF

2023-03-30 12:01:21

SITE LICENSE CORDIC ALGO XP2

2023-03-30 12:02:10

SITE LICENSE CORDIC ALGO XP

2023-03-30 12:02:11

//-------------------------------------------------------------// Designer : W// Date: 2008.12.16// Discription :Cordic with computation of modulus

2014-11-02 20:03:32

請(qǐng)問CORDIC算法用verilog算法實(shí)現(xiàn)時(shí)���,角度累加器中的45度,26.56度����,14.04度怎么跟verilog語言相對(duì)應(yīng)?

2015-07-11 20:18:57

從網(wǎng)上下載的CORDIC例程(應(yīng)輸出正弦波�����,仿真不對(duì))���,求教���,看看問題出在哪里,謝謝!

2016-02-22 11:38:05

CORDIC(Coordinate Rotation Digital Computer)算法即坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算方法�,是 J.D.Volder1于 1959 年首次提出,主要用于三角函數(shù)�����、雙曲線、指數(shù)

2023-08-09 06:45:44

Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)篇教程預(yù)覽地址:鏈接:http://pan.baidu.com/s/1pK8TlcJ密碼:ojrjETree的開發(fā)板開發(fā)了下面17種verilog圖像算法下圖為ETree的FPGA視頻音頻開發(fā)板����,在淘寶店:shop397545458.taobao.com

2017-11-28 22:20:11

本帖最后由 我來看看你在干什么 于 2018-5-15 09:10 編輯

用verilog實(shí)現(xiàn)EMD算法,需要用到三次樣條插值法��,請(qǐng)問有做過類似算法實(shí)現(xiàn)的嗎�����,可以講一下verilog實(shí)現(xiàn)三次樣條插值的思路�,或者相互交流探討一下嗎?

2018-05-13 21:34:56

請(qǐng)問有沒有大神教教我怎么用verilog實(shí)現(xiàn)二維峰值的查找����?峰值即這個(gè)數(shù)比它周圍所有數(shù)都大!

2016-05-26 09:22:37

請(qǐng)教高手:寫FPGA代碼時(shí)�,是先自己畫出電路原理圖或框圖、或流程圖��,再對(duì)照電路框圖寫代碼�;還是不需此過程,直接寫代碼�?���?春枚嗾撐亩际茄芯磕?b class="flag-6" style="color: red">算法實(shí)現(xiàn)的VLSI結(jié)構(gòu)���,故個(gè)人認(rèn)為通常應(yīng)先有電路框圖及結(jié)構(gòu)�,再寫verilog�����,不知對(duì)不對(duì)�����?

2013-05-14 21:04:38

大多數(shù)工程師在碰到需要在 FPGA 中實(shí)現(xiàn)諸如正弦�、余弦或開平方這樣的數(shù)學(xué)函數(shù)時(shí)�����,首先會(huì)想到的是用查找表���,可能再結(jié)合線性內(nèi)插或者冪級(jí)數(shù)(如果有乘法器可用)�����。不過對(duì)這種工作來說,CORDIC 算法

2019-09-19 09:07:16

本次發(fā)布 Gowin CORDIC IP 參考設(shè)計(jì)及用戶指南。Gowin CORDIC IP 的用戶指南及參考設(shè)計(jì)可在高云官網(wǎng)下載�����,其中參考設(shè)計(jì)已配置一例特定參數(shù)����,可用于仿真�,實(shí)例化加插用戶設(shè)計(jì)后的總綜合,總布局布線�����。

2022-10-08 08:11:00

Gowin CORDIC IP用戶指南主要內(nèi)容包括功能特征��、端口描述�����、時(shí)序說明�����、配置調(diào)用、參考設(shè)計(jì)等����。主要用于幫助用戶快速了解 Gowin CORDIC IP的產(chǎn)品特性、特點(diǎn)及使用方法�。

2022-10-08 08:07:55

使用LabVIEW FPGA模塊中的CORDIC IP核,配置arctan(X/Y)算法���,配置完成之后���,IP核只有一個(gè)輸入。我參考網(wǎng)上VHDL CORDIC IP核�����,說是將XY合并了�,高位X低位Y��。不知道在LabVIEW中如何將兩個(gè)值X���、Y合并成一個(gè)(X��、Y均為定點(diǎn)數(shù))��。具體情況如下圖:

2019-09-10 20:07:07

�,各位大神,有人有用Verilog或者VHDL實(shí)現(xiàn)的RSA算法源代碼么�����?小弟急用�,謝謝啦!拜謝���!

2016-05-16 11:08:31

哪位大神做過xilinx的PC-CFR算法的實(shí)現(xiàn)�����,希望能指導(dǎo)一下?�。����?����!

2014-04-03 23:32:21

用vivado2019.2建立工程,工程中調(diào)用cordic IP核進(jìn)行atan求解,功能仿真時(shí)正常且滿足要求���;綜合時(shí)正常����;實(shí)現(xiàn)時(shí)報(bào)錯(cuò)提示多重驅(qū)動(dòng)��。

如果經(jīng)cordic計(jì)算后的輸出值不用于后續(xù)的操作

2023-06-06 17:17:37

在做夏宇聞教材《從算法設(shè)計(jì)到硬線邏輯的實(shí)現(xiàn)》中第十章練習(xí)6-在Verilog HDL中使用函數(shù)按原文編譯總是出錯(cuò)��,將[3:0]中的3改為大于3的值就沒錯(cuò)了����,如[4:0].為什么呢?

2013-11-06 14:14:12

【作者】:張?zhí)扈?【來源】:《武漢理工大學(xué)學(xué)報(bào)》2010年06期【摘要】:傳統(tǒng)CORDIC算法需要通過查找表和許多乘法器才能實(shí)現(xiàn)矩陣的QR分解,這會(huì)導(dǎo)致硬件電路實(shí)現(xiàn)復(fù)雜,運(yùn)算速度降低,此外它能夠計(jì)算

2010-04-24 09:27:51

收機(jī)擴(kuò)頻碼的捕獲以及數(shù)據(jù)解調(diào)性能的影響�����,從而提高接收機(jī)的性能��。頻偏校正電路中通常需要根據(jù)給定相位產(chǎn)生余弦信號(hào)和正弦信號(hào)���,其中最重要的實(shí)現(xiàn)技術(shù)是CORDIC(CoordinateRotationDigitalComputer,坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī))算法。

2019-09-19 07:17:19

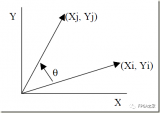

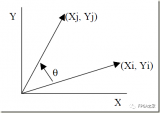

最近出于項(xiàng)目需要�����,對(duì)CORDIC算法深入學(xué)習(xí)下��。剛開始的時(shí)候上網(wǎng)搜了下資料發(fā)現(xiàn)一上來就直接是推導(dǎo)公式����,然后工程運(yùn)用與理論推導(dǎo)聯(lián)系太少感覺無從下手!對(duì)于像我們數(shù)學(xué)丟了很多年的同學(xué)來說實(shí)在是痛苦啊��。好在

2014-08-11 14:05:05

單片機(jī)主要作用是控制外圍的器件�,并實(shí)現(xiàn)一定的通信和數(shù)據(jù)處理。雖然單片機(jī)不擅長(zhǎng)實(shí)現(xiàn)算法和進(jìn)行復(fù)雜的運(yùn)算�����,但在某些特定場(chǎng)合��,不可避免地要用到數(shù)學(xué)運(yùn)算��。比如:在單片機(jī)進(jìn)行數(shù)據(jù)采集時(shí)���,會(huì)遇到數(shù)據(jù)的...

2022-01-07 06:48:00

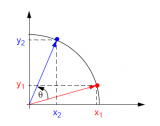

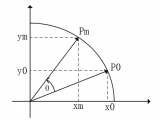

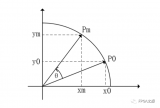

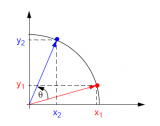

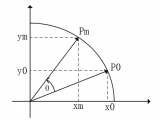

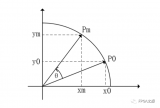

三角函數(shù)和雙曲線函數(shù)的低成本逐次逼近算法��。最初由Jack Volder在1959年提出�,它被廣泛用于早期計(jì)算器當(dāng)中。CORDIC算法通過基本的加和移位運(yùn)算代替乘法運(yùn)算�����,具體原理不在此贅述�����。坐標(biāo)旋轉(zhuǎn)算法示意圖

2022-08-10 14:38:16

�����。我們提出了一種基于CORDIC(坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī))技術(shù)的無開方無除法的MQR陣分解方法�,并應(yīng)用于自適應(yīng)陣抗干擾處理,取得了良好的效果���。CORDIC算法最初由Volder提出����,最早用于三角函數(shù)的計(jì)算

2020-11-23 09:15:32

基于Cordic的正弦信號(hào)發(fā)生器建模仿真(1)信號(hào)頻率范圍10Hz—200KHz���;(2)給出Cordic算法信號(hào)發(fā)生器����;(3)可以隨時(shí)改變頻率控制字或相位控制字��。

2015-07-03 12:40:17

垂直投影進(jìn)行研究�。二、方案基于Verilog的垂直投影的實(shí)現(xiàn)��,考慮使用雙口ram�、fifo/shfit_rams 實(shí)現(xiàn),但是使用ram實(shí)現(xiàn)時(shí)�,由于要操作地址,控制邏輯復(fù)雜�����,而且在寫回時(shí)消耗的拍數(shù)比較

2019-03-03 17:51:01

大家好�,這是一個(gè)UDP實(shí)現(xiàn)的16位定點(diǎn)CORDIC,用于計(jì)算給定角度的正弦和余弦�。它在PSoC 3上被支持,并且可能(忽略警告)運(yùn)行到33 MHz�。我已經(jīng)附上了一個(gè)演示項(xiàng)目與項(xiàng)目庫,所以嘗試運(yùn)行它在

2019-05-24 10:03:12

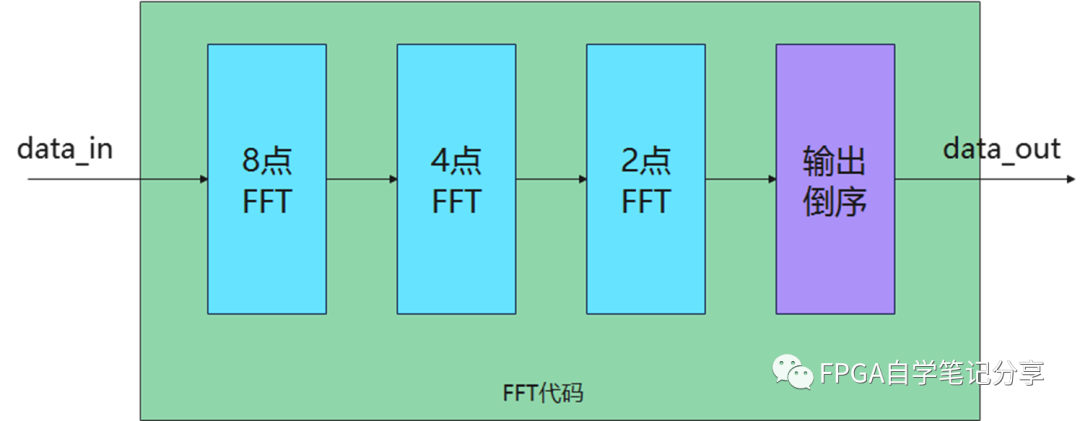

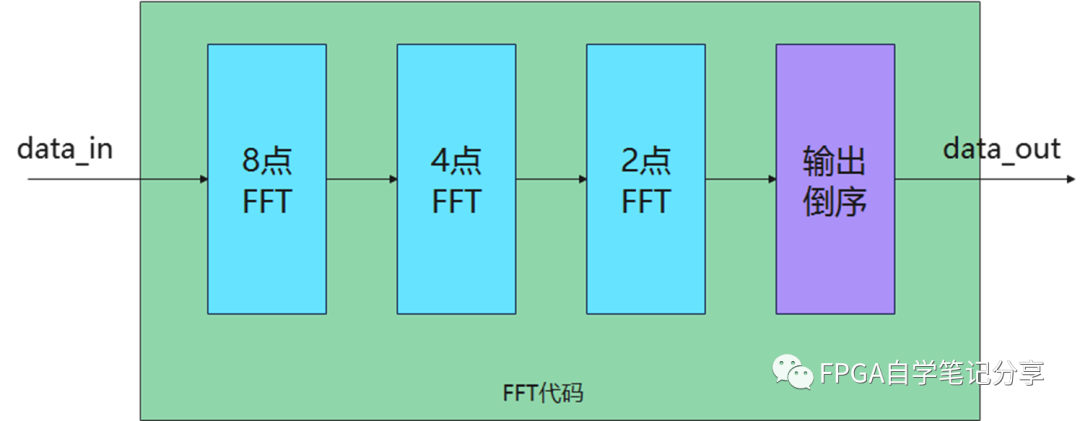

耗費(fèi)了FFT運(yùn)算中大量的乘法器資源���。CORDIC算法只需簡(jiǎn)單的移位與加減運(yùn)算就能實(shí)現(xiàn)向量旋轉(zhuǎn)�����,具有使用資源少�����、硬件規(guī)模小等優(yōu)勢(shì)�。因此在FFT蝶形運(yùn)算中用其代替?zhèn)鹘y(tǒng)FFT運(yùn)算中的復(fù)數(shù)乘法器�����,可以獲得更好

2011-07-11 21:32:29

這是夏老師經(jīng)典的verilog教程���。其名字為:《從算法設(shè)計(jì)到硬線邏輯的實(shí)現(xiàn)》復(fù)雜數(shù)字邏輯系統(tǒng)的VerilogHDL設(shè)計(jì)技術(shù)和方法夏宇聞 編著

2013-09-27 19:38:20

大家好��,我有一個(gè)平方根���,眼壓測(cè)量和許多其他功能在我的程序����。它們使我的程序變慢了����。我聽說過CORDIC函數(shù)���,但我不知道如何實(shí)現(xiàn)它。有人能幫助我嗎�����?我將非常感謝你�����。當(dāng)做阿維斯

2019-10-28 07:56:31

基于線性預(yù)測(cè)的FIR自適應(yīng)語音濾波器的系統(tǒng)結(jié)構(gòu)由那幾部分組成��?如何降低LMS算法的計(jì)算復(fù)雜度�,加快程序在DSP上運(yùn)行的速度���,實(shí)現(xiàn)DSP?

2021-04-12 06:27:49

嗨��,我已經(jīng)實(shí)現(xiàn)了radix2 / 4&在ISE 14.1中沒有使用cordic的分裂基數(shù)FFT算法���。它們運(yùn)行良好... o / p即將到來��,但問題是代碼是不可合成的��。為了使代碼可合成��,我必須

2020-03-06 08:40:29

本文利用CORDIC算法在FPGA上實(shí)現(xiàn)了高速自然對(duì)數(shù)變換器。

2021-04-30 06:05:22

目錄背景AES加密的幾種模式基本運(yùn)算AES加密原理Matlab實(shí)現(xiàn)Verilog實(shí)現(xiàn)Testbench此文重點(diǎn)講述了AES加密算法的加密模式和原理,用MATLAB和Verilog進(jìn)行加解密的實(shí)現(xiàn)�。美

2021-07-28 07:34:30

有誰做過對(duì)稱矩陣特征值分解的FPGA實(shí)現(xiàn)的么?網(wǎng)上查了很多資料好多都是零幾年的論文�����,有用到cordic算法,希望有做過的能夠提供個(gè)verilog代碼供我學(xué)習(xí)���,謝過了~

2016-11-07 23:16:45

謝謝各位�。���。各位大神。�。用fpga實(shí)現(xiàn)FFT算法,最好是verilog hdl的�。?�;蛘咄扑]一些好書��。�����。

2013-05-06 00:24:19

如何使用Verilog硬件描述語言實(shí)現(xiàn)AES密碼算法?

2021-04-14 06:29:10

正在做一個(gè)課題,用FPGA控制AD9910��,但是本人想把基于ROM表的改成基于CORDIC算法的���,這樣還能不能用FPGA實(shí)現(xiàn)控制AD9910���,理論上應(yīng)該可以的,但是不知道這樣有沒有意義一般都是直接用

2018-12-01 08:47:01

分析了CORDIC算法的基本原理和MVR-CODIC算法的特點(diǎn)��。在此基礎(chǔ)上���,提出了一種改進(jìn)型MVR-CODIC算法���,利用查ROM表代替原算法中比例因子的計(jì)算方法,討論了改進(jìn)后算法的所需ROM表的容

2009-03-04 22:26:26 28

28 針對(duì)在工業(yè)中越來越多的使用到的FFT�����,本文設(shè)計(jì)出了一種利用CORDIC 算法在FPGA 上實(shí)現(xiàn)快速FFT 的方法�����。CORDIC 實(shí)現(xiàn)復(fù)數(shù)乘法比普通的計(jì)算器有結(jié)構(gòu)上的優(yōu)勢(shì),并且采用了循環(huán)結(jié)構(gòu)

2009-08-24 09:31:10 9

9 CORDIC 算法在通信和圖像處理等各個(gè)領(lǐng)域有著廣泛的應(yīng)用���,但是浮點(diǎn)CORDIC 由于迭代延時(shí)大且實(shí)現(xiàn)復(fù)雜沒有得到很好的應(yīng)用���,本文提出了一種修正浮點(diǎn)CORDIC 算法: 高精度順序迭代HPOR

2009-12-15 14:27:24 14

14 基于CORDIC 算法的NCO 實(shí)現(xiàn)田力, 馮琦(西安電子科技大學(xué) 電路設(shè)計(jì)研究所����,陜西 西安 710071)摘要:NCO 在信號(hào)處理方面有著廣泛的應(yīng)用。而函數(shù)發(fā)生器是NCO 中的關(guān)鍵部分����,

2009-12-15 14:30:33 23

23 針對(duì)在工業(yè)中越來越多的使用到的FFT�,本文設(shè)計(jì)出了一種利用CORDIC算法在FPGA上實(shí)現(xiàn)快速FFT的方法。CORDIC實(shí)現(xiàn)復(fù)數(shù)乘法比普通的計(jì)算器有結(jié)構(gòu)上的優(yōu)勢(shì)�����,并且采用了循環(huán)結(jié)構(gòu)的CORDIC算

2010-08-09 15:39:20 55

55 CORDIC算法是用于計(jì)算三角����、反三角、指數(shù)�、對(duì)數(shù)等超越函數(shù)的簡(jiǎn)捷算法。將該算法應(yīng)用在以單片機(jī)為核心的三軸電子羅盤中,用于實(shí)現(xiàn)羅盤的傾斜補(bǔ)償并計(jì)算俯仰角���、橫滾角和航向

2010-10-18 16:52:57 0

0 復(fù)雜數(shù)字邏輯系統(tǒng)的Verilog

2010-11-01 17:03:59 0

0 用Verilog實(shí)現(xiàn)8255芯片功能

2010-11-03 17:06:09 144

144 研究了一種利用CORDIC算法的矢量及旋轉(zhuǎn)模式對(duì)載波同步中相位偏移進(jìn)行估計(jì)并校正的方法�。設(shè)計(jì)并實(shí)現(xiàn)了基于CORDIC算法的數(shù)字鎖相環(huán)����。通過仿真,驗(yàn)證了設(shè)計(jì)的有效性和高效性�。

2010-12-15 14:49:43 0

0 本文提出了應(yīng)用CORDIC(Coordinate Rotation Digital Computer)算法實(shí)時(shí)計(jì)算正弦值的方案,并基于CORDIC算法在FPGA芯片上設(shè)計(jì)了2FSK調(diào)制器�����。這不僅能夠節(jié)省大量的FPGA邏輯資源����,而且能很好地兼顧速度

2011-05-31 10:22:06 1508

1508

CORDIC算法將復(fù)雜的算術(shù)運(yùn)算轉(zhuǎn)化為簡(jiǎn)單的加法和移位操作,然后逐次逼近結(jié)果����。這種方法很好的兼顧了精度、速度和硬件復(fù)雜度�,它與VLSI技術(shù)的結(jié)合對(duì)DSP算法的硬件實(shí)現(xiàn)具有極大的意義

2011-06-27 17:27:26 66

66 摘要: 傳統(tǒng)的基于查表法的數(shù)控振蕩器耗費(fèi)大量的FPGA片內(nèi)資源。為了解決這一問題���,提出了一種基于CORDIC(coordinate rotation digital compute�,坐標(biāo)旋轉(zhuǎn)數(shù)值計(jì)算)算法的數(shù)控振蕩器的設(shè)計(jì)方

2012-05-28 16:04:59 39

39 摘要: 傳統(tǒng)的基于查表法的數(shù)控振蕩器耗費(fèi)大量的FPGA片內(nèi)資源。為了解決這一問題���,提出了一種基于CORDIC(coordinate rotation digital compute�,坐標(biāo)旋轉(zhuǎn)數(shù)值計(jì)算)算法的數(shù)控振蕩器的設(shè)計(jì)方

2012-05-29 16:46:34 0

0 為了滿足現(xiàn)代高速通信中頻率快速轉(zhuǎn)換的需求�����,基于坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算(CORDIC���,Coordinate Rotation Digital Computer)算法完成正交直接數(shù)字頻率合成(ODDFS����,Orthogonal Direct Digital Frequency Synthes

2013-02-22 16:26:46 34

34 verilog verilog verilog verilog verilog verilog verilog verilog

2015-11-12 14:43:51 0

0 數(shù)字系統(tǒng)設(shè)計(jì):VERILOG實(shí)現(xiàn) (第2版)

2015-11-30 10:21:33 0

0 論文闡述了CORDIC 算法的基本原理����,在旋變解碼�����、坐標(biāo)變換���、SVPWM�����、輸出限幅等算法中的應(yīng)用�,并給出了實(shí)現(xiàn)方法及運(yùn)算值與實(shí)際值的對(duì)比,證明了CORDIC 算法具有運(yùn)算精度高����,占用資源少,運(yùn)算速度快等特點(diǎn)��。最后通過一臺(tái)額定9kW 的電動(dòng)車用永磁同步電機(jī)實(shí)驗(yàn)驗(yàn)證了算法的正確性和實(shí)用性��。

2016-08-03 18:36:25 25

25 cordic算法verilog實(shí)現(xiàn)(簡(jiǎn)單版)(轉(zhuǎn)載)module cordic(clk, phi, cos, sin); parameter W = 13, W_Z = 14; input clk; input [W_Z-1:0] phi; output[W-1:0]

2017-02-11 03:06:11 3044

3044

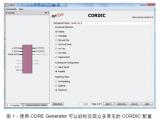

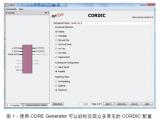

以ISE10.1軟件為例���,其集成的CORDIC算法IP為V3.0版本����,具體步驟如下:

2017-02-11 11:16:49 2627

2627

CORDIC是在沒有專用乘法器(最小化門數(shù)量)情況下�,一組完成特定功能的算法,包括平方���、超越����、Log、sin/cos/artan���。原理為連續(xù)的旋轉(zhuǎn)一個(gè)較小的角度�����,以一定精度逼近想要的角度��。

2017-02-11 19:24:06 5373

5373 針對(duì)傳統(tǒng)CORDIC算法流水線結(jié)構(gòu)的迭代次數(shù)過多�,運(yùn)算速度不夠快����,消耗硬件資源較多的缺點(diǎn),改進(jìn)了一種基于旋轉(zhuǎn)模式并行運(yùn)算的CORDIC算法�。該算法采用二進(jìn)制兩極編碼和微旋轉(zhuǎn)角編碼進(jìn)行低位符號(hào)預(yù)測(cè)

2017-11-16 10:46:22 14

14 的應(yīng)用。因?yàn)?b class="flag-6" style="color: red">Cordic 算法只用了移位和加法�,很容易用純硬件來實(shí)現(xiàn),因此我們常能在FPGA運(yùn)算平臺(tái)上見到它的身影��。不過�����,大多數(shù)的軟件程序員們都沒有聽說過這種算法��,也更不會(huì)主動(dòng)的去用這種算法�����。

2017-11-17 16:37:01 6470

6470

雖然CORDIC 是實(shí)現(xiàn) DSP 和數(shù)學(xué)函數(shù)最重要的算法之一��,但許多設(shè)計(jì)人員并不熟悉�����。 作者:Adam P. Taylor 首席工程師 阿斯特里姆公司 (EADS Astrium

2019-10-06 10:52:00 1565

1565

使用Verilog描述硬件的基本設(shè)計(jì)單元是模塊(module)���。構(gòu)建復(fù)雜的電子電路�����,主要是通過模塊的相互連接調(diào)用來實(shí)現(xiàn)的�����。模塊被包含在關(guān)鍵字module���、endmodule之內(nèi)�����。實(shí)際的電路元件�����。Verilog中的模塊類似C語言中的函數(shù)

2017-12-08 17:20:57 9710

9710 描述了浮點(diǎn)型算法的加、減�����、乘�、除的verilog代碼,編寫了6位指數(shù)位,20位小數(shù)位的功能實(shí)現(xiàn)并且通過仿真驗(yàn)證

2018-01-16 14:15:54 1

1 本文是基于FPGA實(shí)現(xiàn)Cordic算法的設(shè)計(jì)與驗(yàn)證����,使用Verilog HDL設(shè)計(jì)����,初步可實(shí)現(xiàn)正弦、余弦����、反正切函數(shù)的實(shí)現(xiàn)。將復(fù)雜的運(yùn)算轉(zhuǎn)化成FPGA擅長(zhǎng)的加減法和乘法����,而乘法運(yùn)算可以用移位運(yùn)算代替

2018-07-03 10:18:00 2349

2349

為提高圖像邊緣檢測(cè)的處理速度,提出一種基于CORDIC的高速Sobel算法實(shí)現(xiàn)�����。

2018-10-05 09:54:00 3279

3279

CORDIC(Coordinate Rotation Digital Computer)算法即坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算方法���,是J.D.Volder1于1959年首次提出��,主要用于三角函數(shù)����、雙曲線、指數(shù)���、對(duì)數(shù)

2019-11-13 07:09:00 6100

6100 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog的學(xué)習(xí)PPT課件合集免費(fèi)下載包括了:從算法設(shè)計(jì)到硬線邏輯的實(shí)現(xiàn)�����,復(fù)雜數(shù)字邏輯系統(tǒng)的Verilog HDL設(shè)計(jì)方法簡(jiǎn)介���,示例,語法的資料合集���。

2020-04-30 08:00:00 6

6 函數(shù)和算術(shù)操作的循環(huán)迭代算法�����。CORDIC 算法主要由加法�����、移位實(shí)現(xiàn)�,從而大大降低了占用的FPGA 資源�����。該文介紹一種由CORDIC 算法推導(dǎo)的對(duì)數(shù)函數(shù)在FPGA 上的實(shí)現(xiàn)。

2020-08-07 17:14:00 12

12 主要介紹了坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算(CORDIC)算法在US�,g,鑒別器中的應(yīng)用����,包括碼跟蹤環(huán)��、鎖頻環(huán)和鎖相環(huán)鑒別器���,并進(jìn)行了FPGA實(shí)現(xiàn)�����。在設(shè)計(jì)中����,采用統(tǒng)一cORDIc算法優(yōu)化方法減少硬件開銷����,用非流水

2021-01-22 16:12:00 8

8 提出了一種基于流水線CORDIC的算法實(shí)現(xiàn)QAM調(diào)制,可有效節(jié)省硬件資源�,提高運(yùn)算速度��。用Verilog HDL對(duì)本設(shè)計(jì)進(jìn)行了編程和功能仿真�����,仿真結(jié)果表明���,本設(shè)計(jì)具有一定的實(shí)用性。

2021-02-01 14:54:02 6

6 迭代方程里���,從而額提出了一種統(tǒng)一的CORDIC算法形式���。 CORDIC算法的核心是利用加法和移位的迭代操作去替代復(fù)雜的運(yùn)算,從而非常有

2021-04-11 11:16:50 12485

12485

FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)(單片機(jī)電源維修)-該文檔為FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)資料����,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 任何適合產(chǎn)品實(shí)現(xiàn)的算法���,都是將簡(jiǎn)易實(shí)現(xiàn)作為第一目標(biāo)�。CORDIC算法是建立在適應(yīng)性濾波器���、FFT���、解調(diào)器等眾多應(yīng)用基礎(chǔ)上計(jì)算超越函數(shù)的方法�。其核心思想是二分逐次逼近�����。???? CORDIC

2021-08-16 11:21:11 1827

1827

算法之空間復(fù)雜度:衡量一個(gè)算法運(yùn)行需要開辟的額外空間

2022-08-31 10:29:40 1260

1260 在FPGA硬件實(shí)現(xiàn)CORDIC的邏輯其實(shí)是很簡(jiǎn)單的�,就是設(shè)置好輸入輸出的位寬,然后建立好對(duì)應(yīng)的精度表��,通過旋轉(zhuǎn)加得到運(yùn)算結(jié)果���。

2022-10-17 11:58:58 2049

2049 然而再復(fù)雜的算法����,在設(shè)計(jì)工程師的眼里,也就是一堆數(shù)學(xué)公式����,算法設(shè)計(jì)者也應(yīng)該盡量做簡(jiǎn)單的算法實(shí)現(xiàn),比如除法��,求冪次方���、開平方等復(fù)雜運(yùn)算到了設(shè)計(jì)工程師這里都已經(jīng)轉(zhuǎn)化成了簡(jiǎn)單的乘法和加法運(yùn)算�����。更復(fù)雜的就是累加�、累乘(我所能接觸到的)。

2022-11-03 15:38:20 623

623 在信號(hào)處理領(lǐng)域���,CORDIC(Coordinate Rotation Digital Computer��,坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī))算法具有重大工程意義����。

2023-03-28 09:39:03 1099

1099 上文基2FFT的算法推導(dǎo)及python仿真推導(dǎo)了基2FFT的公式����,并通過python做了算法驗(yàn)證,本文使用verilog實(shí)現(xiàn)8點(diǎn)基2FFT的代碼�。

2023-06-02 12:38:57 630

630

CORDIC(Coordinate Rotation Digital Computer)算法即坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算方法���,是J.D.Volder1于1959年首次提出�����,主要用于三角函數(shù)�����、雙曲線�����、指數(shù)����、對(duì)數(shù)的計(jì)算。

2023-08-31 14:54:21 1106

1106

由于在項(xiàng)目中需要使用的MPU6050��,進(jìn)行姿態(tài)解算����,計(jì)算中設(shè)計(jì)到arctan 和 sqr(x*2 + y * 2),這兩部分的計(jì)算���,在了解了一番之后�,發(fā)現(xiàn)Cordic算法可以很方便的一次性求出這兩個(gè)這兩部分的計(jì)算�。

2023-09-27 09:30:26 685

685

電子發(fā)燒友網(wǎng)站提供《基于流水線CORDIC算法通用數(shù)字調(diào)制器的FPGA實(shí)現(xiàn)方案.pdf》資料免費(fèi)下載

2023-10-27 09:46:19 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論