Efinity debuger常見問題總結(jié)-v4

? 把燒寫文件和json文件提供給他人進(jìn)行調(diào)試 該方法是在不需要要提供源文件的情況下可以提供給別進(jìn)行....

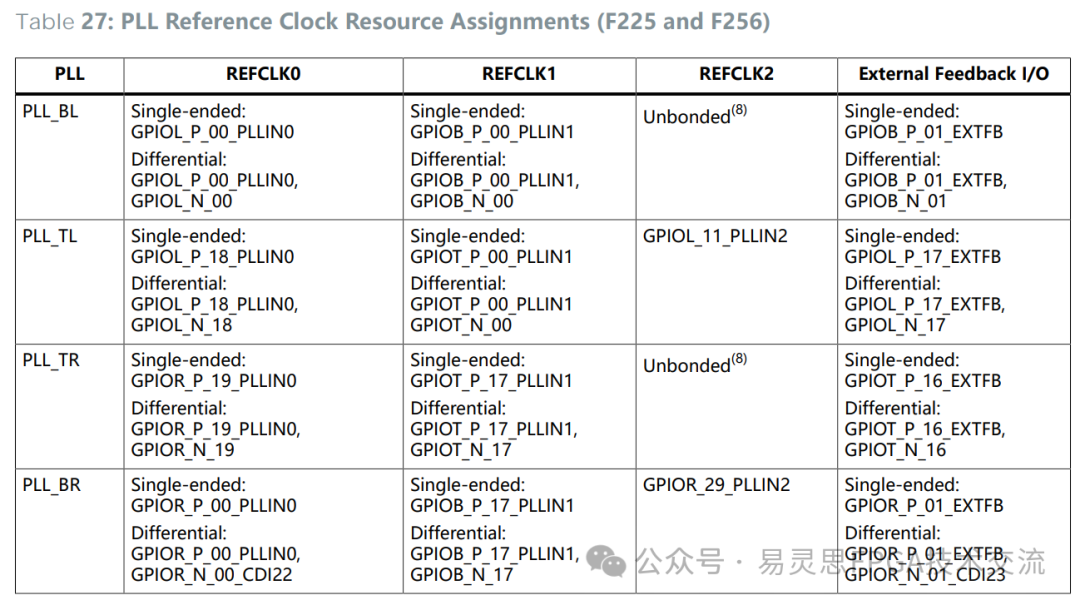

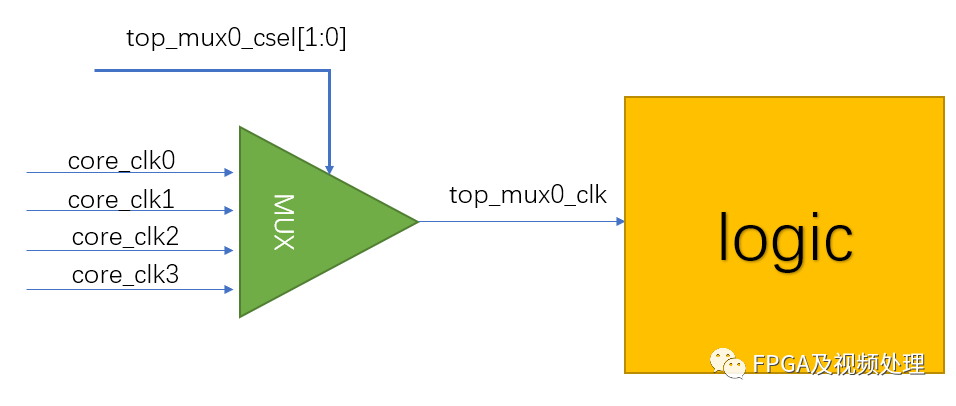

易靈思鈦金系列時(shí)鐘選擇功能-2 以Ti60F225為例來介紹如何實(shí)現(xiàn)下面的4選擇1時(shí)鐘選擇功能

在trion要實(shí)現(xiàn)一個(gè)4選1時(shí)鐘復(fù)用或許比較麻煩。但是在鈦鑫上已經(jīng)給出了解決方案。這里以Ti60F2....

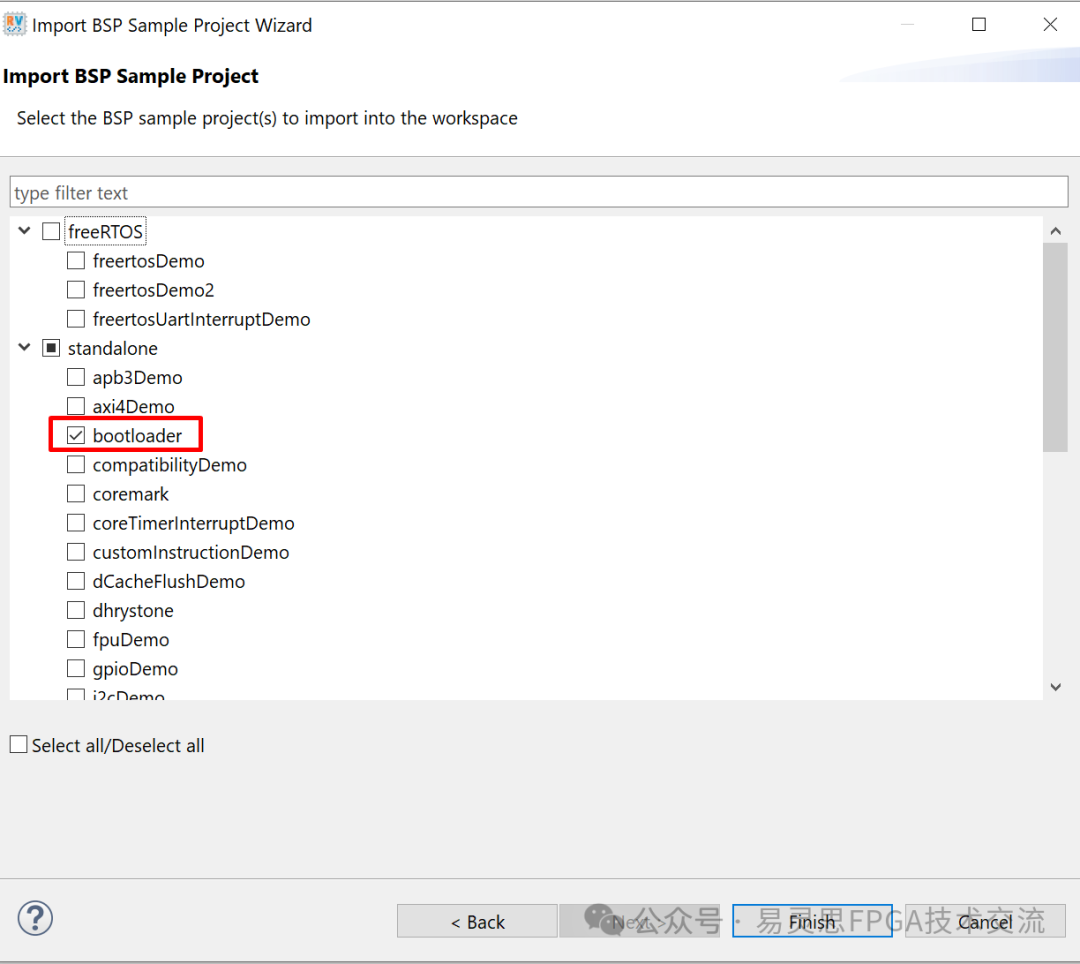

自定義RISC V的bootloader-v3

自定義RISC V的bootloader-v3

在生成SoC時(shí),會(huì)生成一個(gè)預(yù)定義bootloader .bin文件,用于指定soc的工程運(yùn)行的地址,....

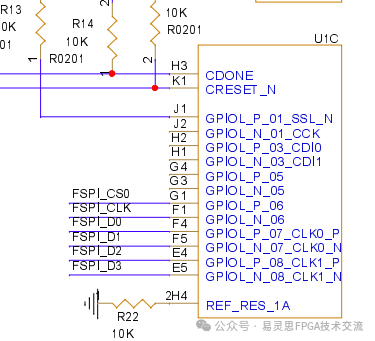

采用易靈思Ti60F100的Ti60F100I3評(píng)估板詳解

采用易靈思Ti60F100的Ti60F100I3評(píng)估板詳解

簡(jiǎn)介? ?? TI60F100-DK是一款采用易靈思Ti60F100開發(fā)的評(píng)估板。 采用底板和核心板....

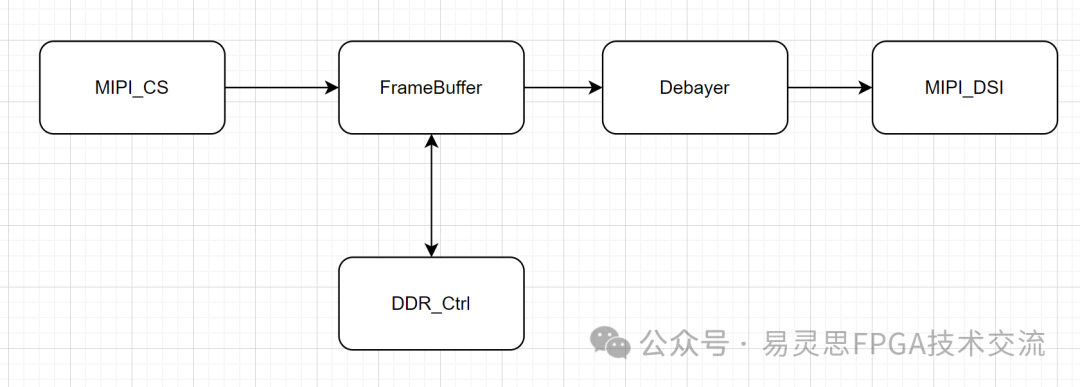

MIPI2.5G DPHY CSI2DSI demo移植 -v1

MIPI2.5G DPHY CSI2DSI demo移植 -v1

最近陸續(xù)有客戶在評(píng)估易靈思的Ti180。Ti180的MIPI 2.5G是硬核。今天做一個(gè)簡(jiǎn)單的移植來....

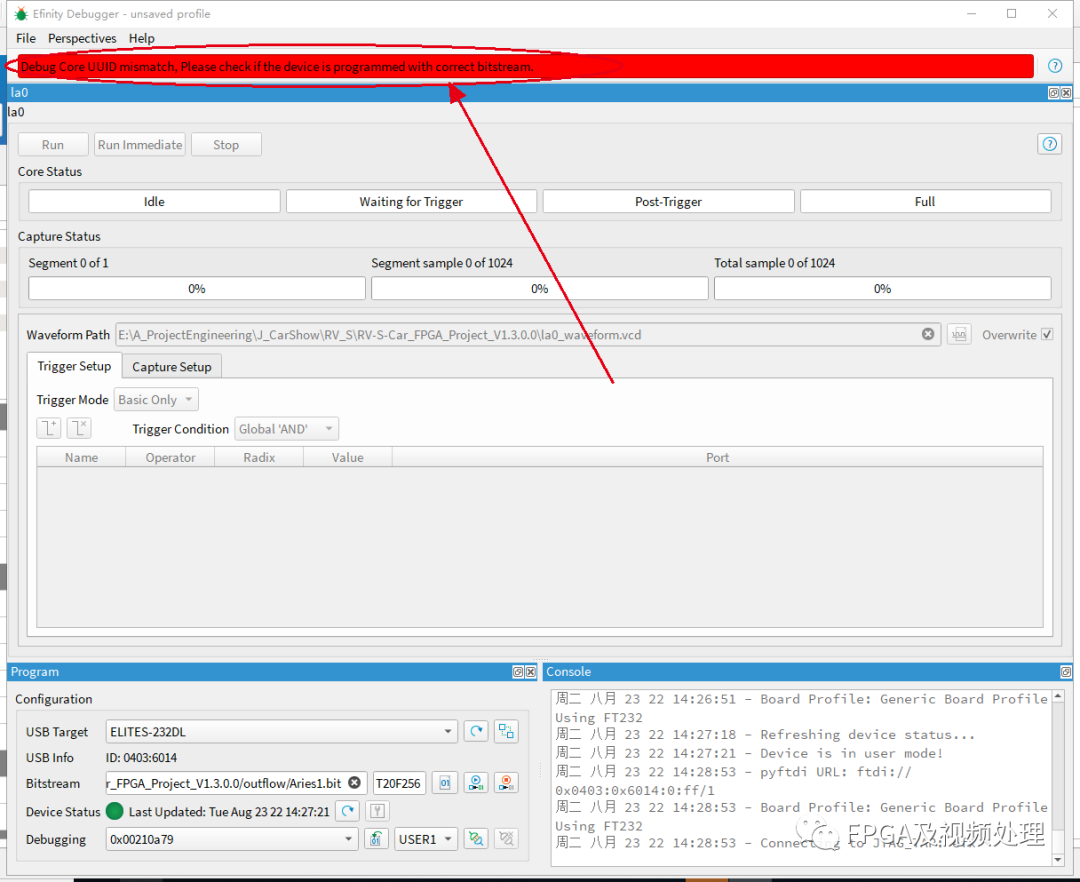

Efinity debuger常見問題總結(jié)-v3

Efinity debuger常見問題總結(jié)-v3

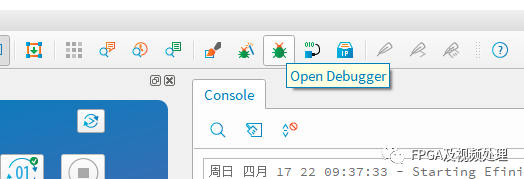

? (1)UUID mismatch Efinity在Debug時(shí)會(huì)出現(xiàn)UUID mismatch錯(cuò)....

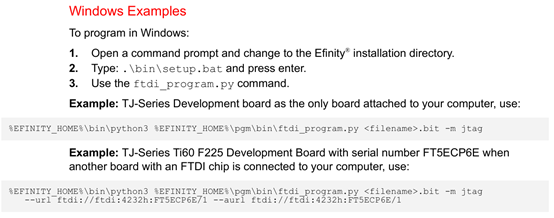

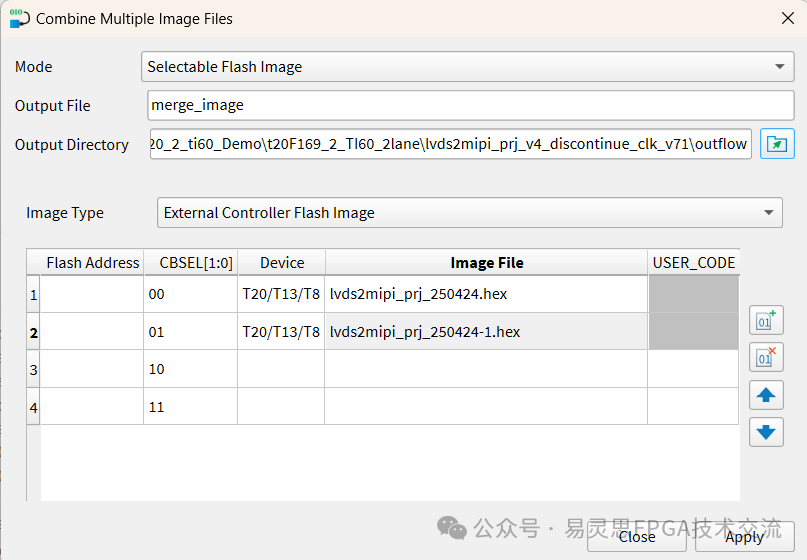

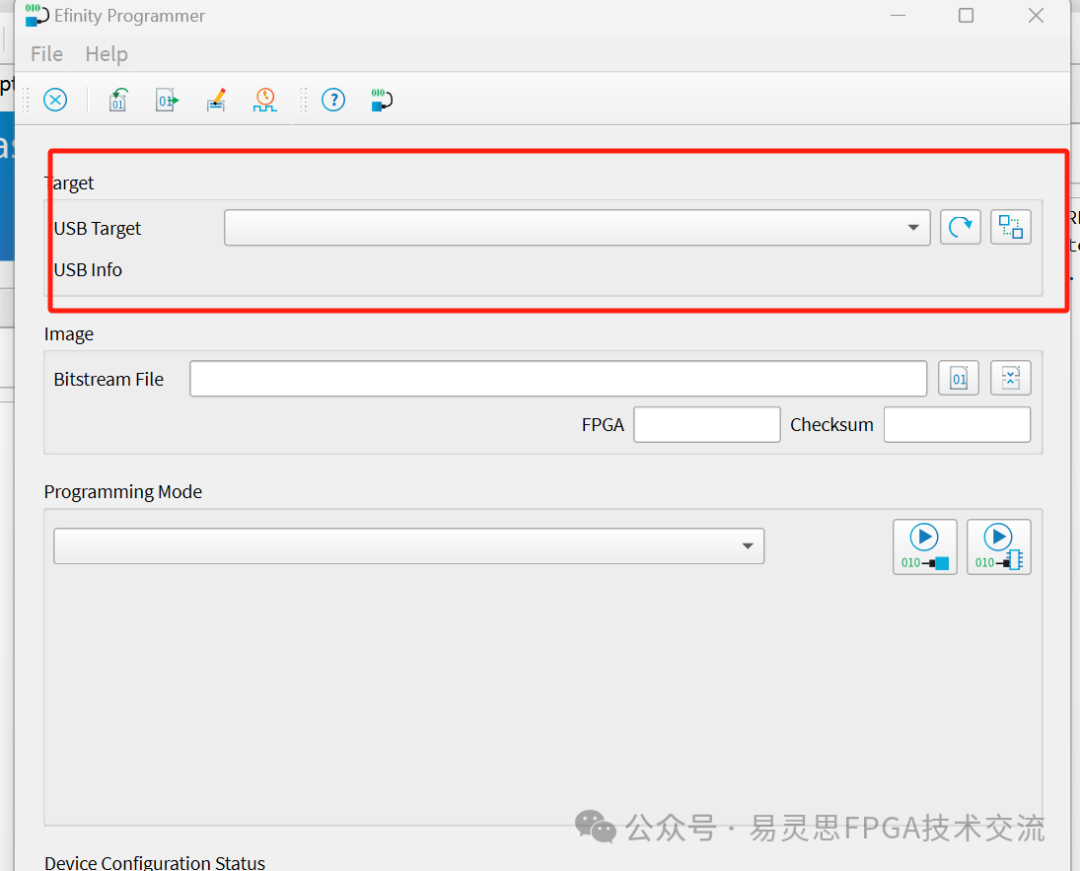

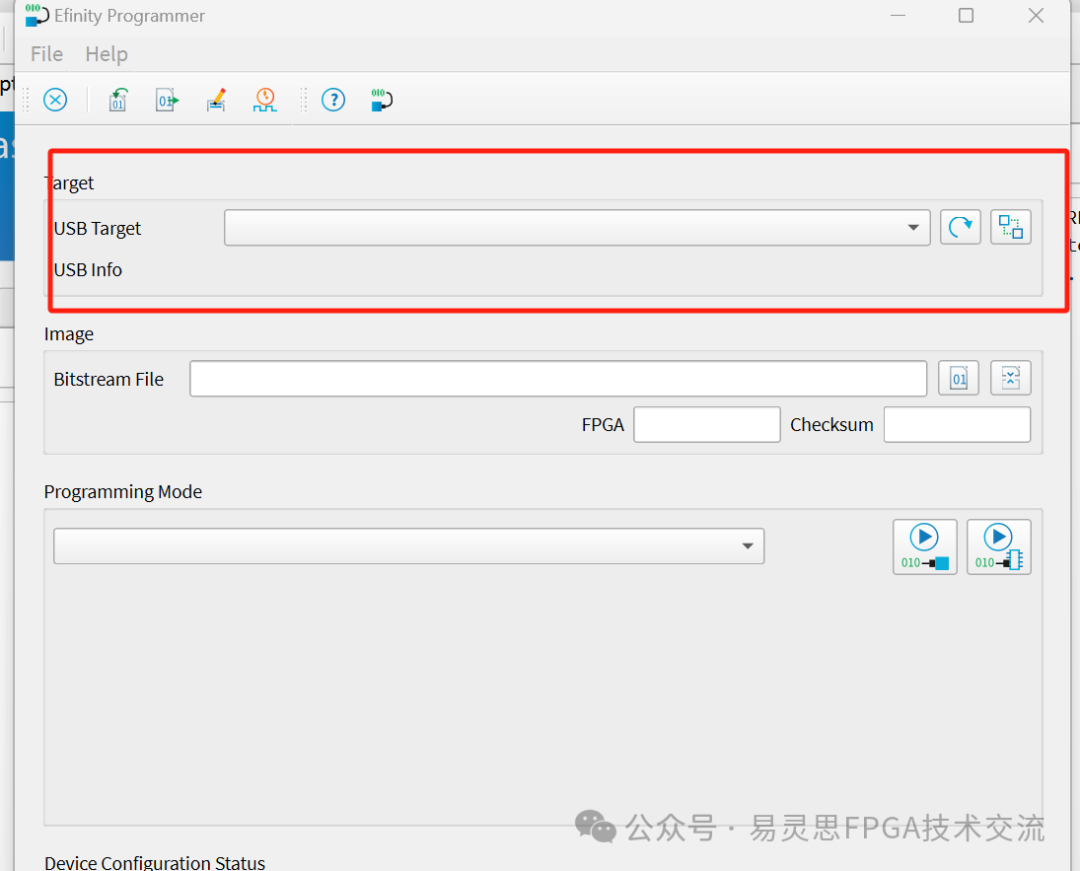

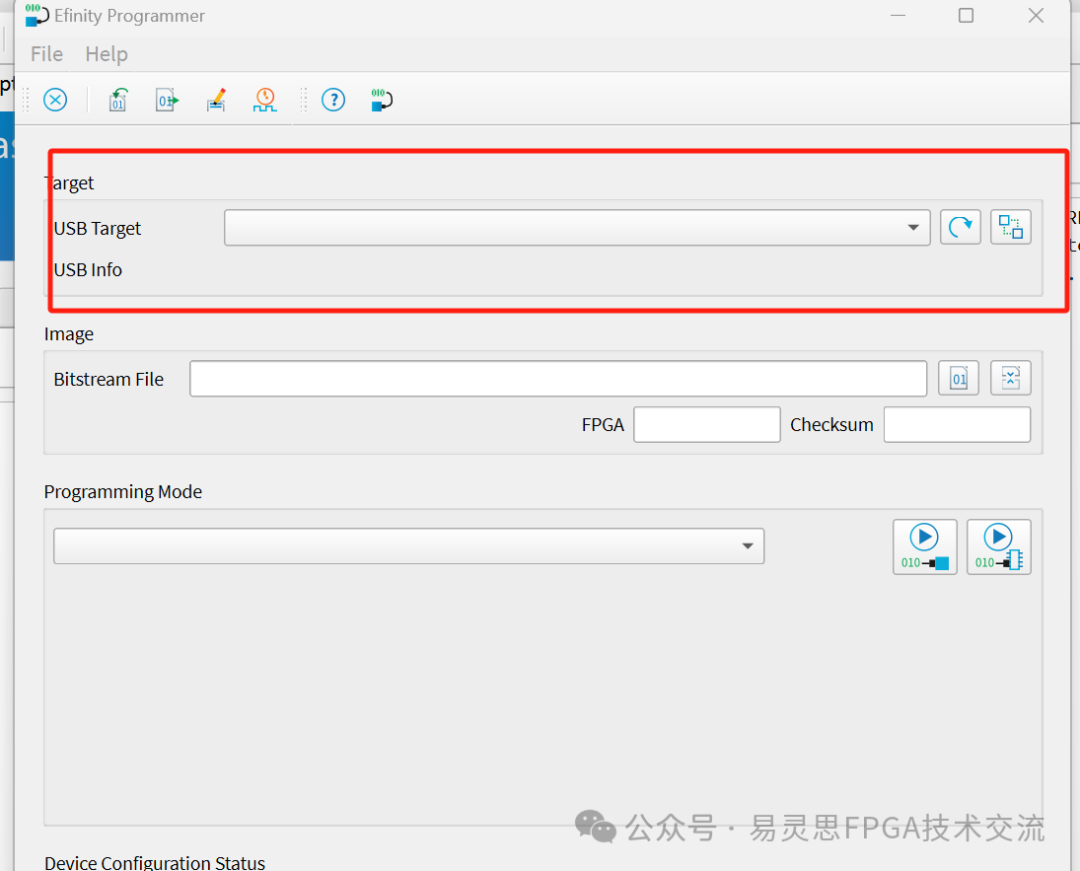

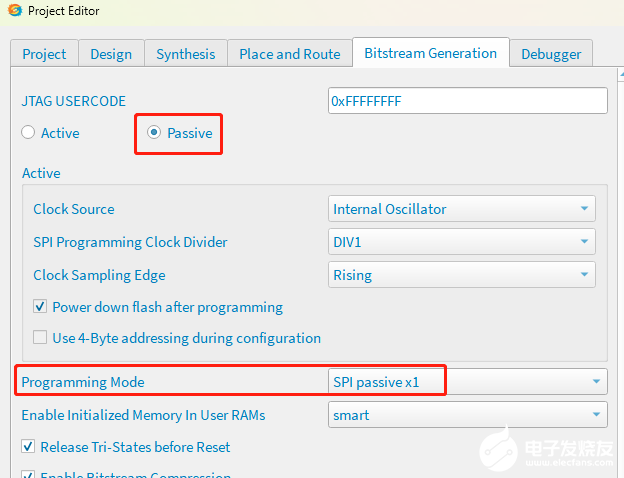

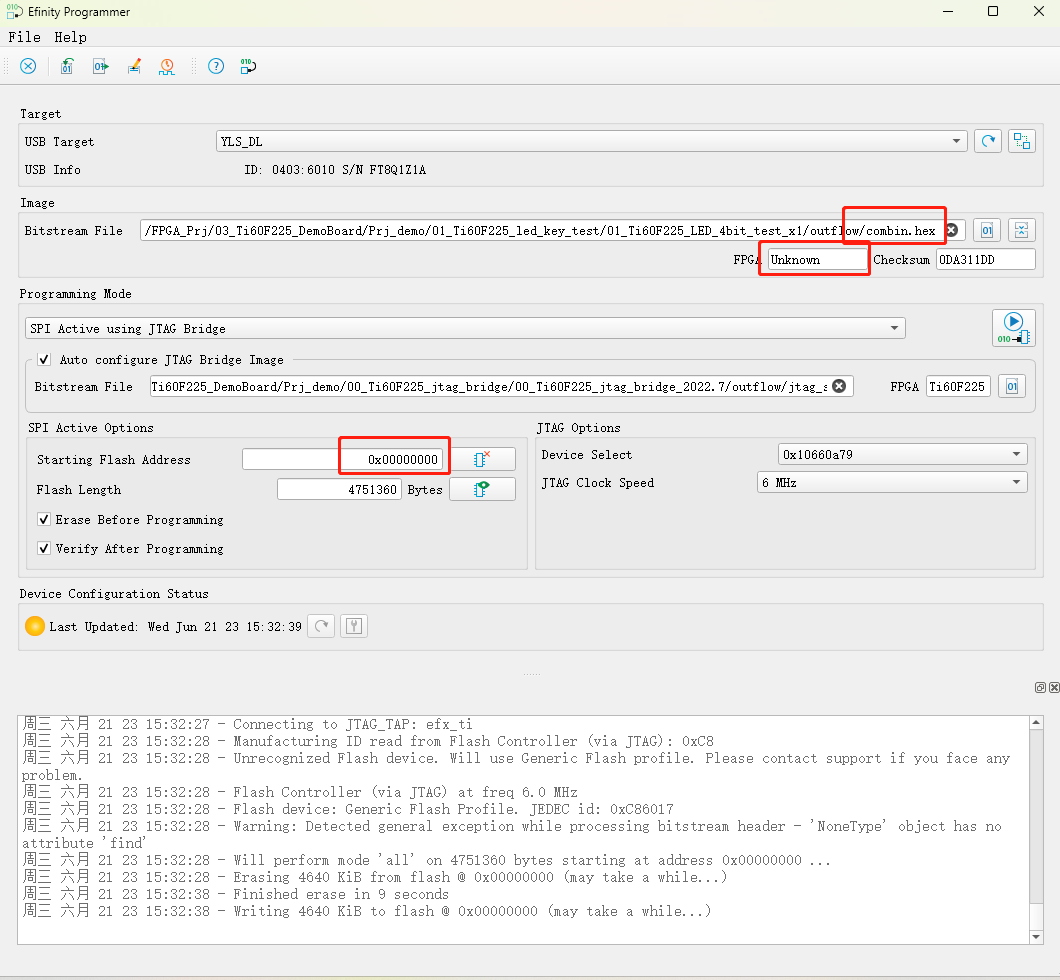

programmer燒寫用戶數(shù)據(jù)到flash-v1

programmer燒寫用戶數(shù)據(jù)到flash-v1

今天有客戶提出怎樣把用戶數(shù)據(jù)寫入到flash的操作,本來以為寫的programmer都不支持了,但是....

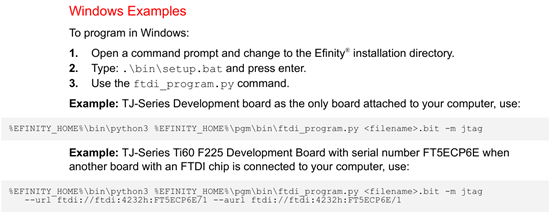

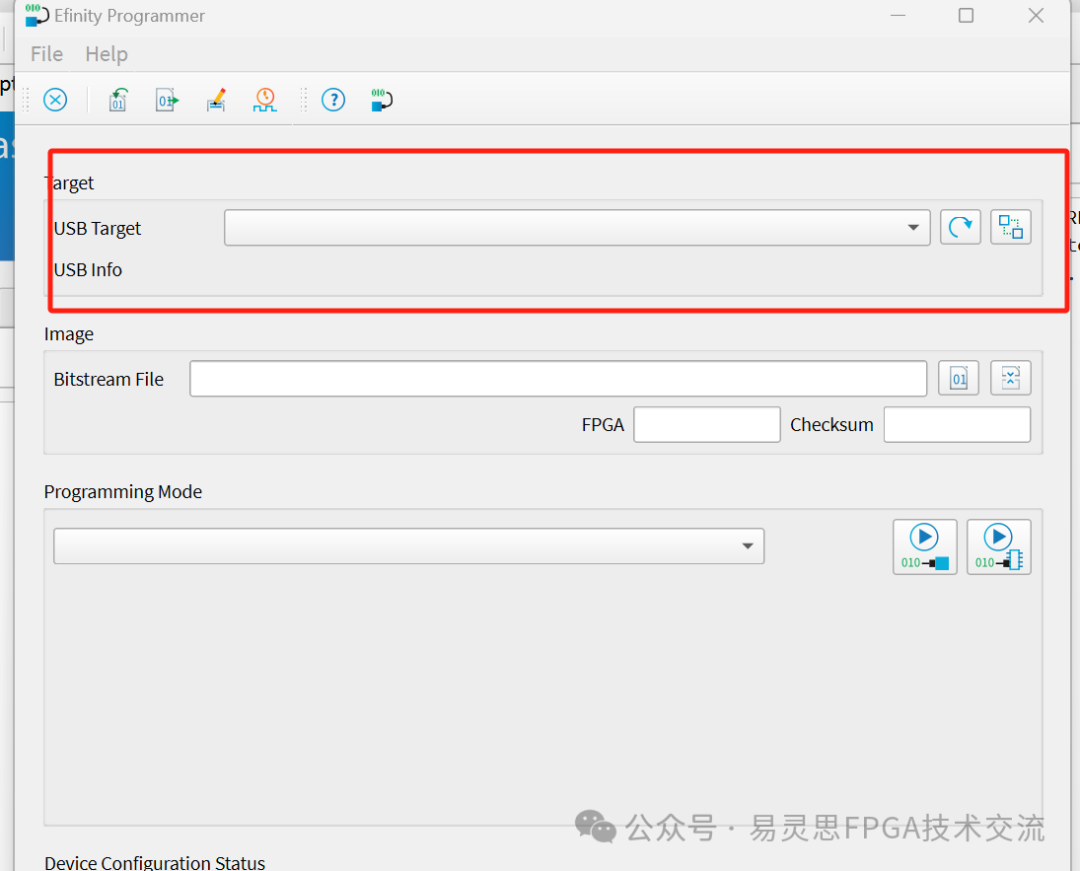

Efinity入門使用-v2

1、 軟件預(yù)設(shè)置2、新建工程3、添加源文件4、添加管腳約束5、添加GPIO6、PLL設(shè)置7、添加debug8、

Efinity入門使用-v4

一、 軟件預(yù)設(shè)置二、新建工程三、添加源文件四、添加管腳約束五、添加GPIO六、PLL設(shè)置七、IPM添加IP八、

Efinity入門使用-v3

1、 軟件預(yù)設(shè)置2、新建工程3、添加源文件4、添加管腳約束5、添加GPIO6、PLL設(shè)置7、添加debug8、

RISC V的I2C操作

RISC V的I2C操作

接口處理top接口output ? ? ?system_i2c_0_io_sda_writeEnable,ou

RISCV 操作常見問題集 - v5

RISCV 操作常見問題集 - v5

(1)如果工程直接復(fù)制另一個(gè)工程,路徑一定要修改,建議重新eclipse工程。(2)clean Project

Efinity RISC-V IDE入門使用-4

Efinity RISC-V IDE入門使用-4

一、Efinity工程io_memoryClk是與存儲(chǔ)器接口共用的時(shí)鐘,需要連接正確。UART由于鈦金系列是有

SOC GPIO操作

SOC GPIO操作

sapphire Soc提供了兩個(gè)GPIO組每組有4個(gè)GPIO,定義為GPIO[3:0],其中只有GPIO[1

RISCV 操作常見問題集 - v4

RISCV 操作常見問題集 - v4

(1)如果工程直接復(fù)制另一個(gè)工程,路徑一定要修改,建議重新eclipse工程。(2)clean Project

Efinity軟件安裝-v5

Efinity軟件安裝-v5

感謝朋友提供的視頻。1、軟件下載易靈思管網(wǎng)地址為https://www.elitestek.com最近一段時(shí)間