如何使用Synopsys VCS仿真器進行ZYNQ BFM IPI設(shè)計仿真

了解如何使用Vivado中的Synopsys VCS仿真器使用ZYNQ BFM IPI設(shè)計運行仿真。....

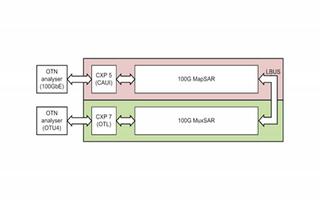

Xilinx的2x100G MuxMapSAR參考設(shè)計

了解Xilinx的2x100G MuxMapSAR參考設(shè)計,該設(shè)計在VC730 OTN測試開發(fā)平臺上....

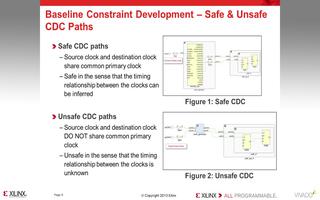

用于定時關(guān)閉的UltraFast Vivado設(shè)計方法

本培訓(xùn)中概述的方法將使您能夠?qū)崿F(xiàn)時序收斂的“簽核”質(zhì)量XDC約束。

無論復(fù)雜程度如何,這種方法還可....

如何使用Xilinx SDK啟動電路板及利用Zynq DRAM進行測試

在本視頻中,我們將學(xué)習(xí)如何使用Xilinx SDK啟動電路板,利用每個驅(qū)動程序提供的應(yīng)用示例并測試各....

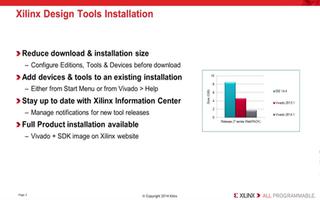

Vivado 2014.1的下載與安裝概述

隨著Vivado 2014.1的發(fā)布,安裝將比以往更小,更快。

您現(xiàn)在可以通過選擇,下載和僅安裝設(shè)....

如何使用Vivado功能創(chuàng)建AXI外設(shè)

了解如何使用Vivado的創(chuàng)建和封裝IP功能創(chuàng)建可添加自定義邏輯的AXI外設(shè),以創(chuàng)建自定義IP。

如何使用時序約束向?qū)?/a>

了解時序約束向?qū)绾斡糜凇巴耆奔s束您的設(shè)計。

該向?qū)ё裱璘ltraFast設(shè)計方法,定義您的時鐘....

采用XilinxVirtex-7 FPGA的12.5Gb/s HMC接口演示

觀看業(yè)界首款采用XilinxVirtex?-7 FPGA的12.5 Gb / s混合存儲器立方體(H....

了解UltraScale DSP架構(gòu)如何降低設(shè)計功耗

了解UltraScale DSP架構(gòu)及其如何幫助降低設(shè)計功耗,以及UltraScale時鐘架構(gòu)中的省....

如何運行UltraScale PCI Express解決方案的四個主要數(shù)據(jù)接口

了解UltraScale PCI Express解決方案的四個主要數(shù)據(jù)接口如何運行。

具有四個獨立....

新UltraScale ASIC時鐘架構(gòu)的使用及好處

了解新的UltraScale ASIC時鐘架構(gòu):如何使用它,它帶來的好處以及從現(xiàn)有設(shè)計遷移的容易程度....

工業(yè)物聯(lián)網(wǎng)的最新趨勢的討論

賽靈思連接與控制總監(jiān)Dan Isaacs在本視頻與您討論了工業(yè)物聯(lián)網(wǎng)的最新趨勢,并講解了賽靈思解決方....

基于視頻/視覺的系統(tǒng)發(fā)展最新趨勢的討論

賽靈思廣播與專業(yè)音視頻業(yè)務(wù)部總監(jiān)Aaron Behman在本視頻中與您一起討論基于視頻/視覺的系統(tǒng)發(fā)....