本視頻概述了基本約束管理的概念,并演示如何創(chuàng)建和管理約束密集型、高度約束的PCB設(shè)計(jì)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

pcb

+關(guān)注

關(guān)注

4319文章

23099瀏覽量

397886 -

視頻

+關(guān)注

關(guān)注

6文章

1945瀏覽量

72910

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

的輸出,對(duì)于Ultrascale和Ultrascale+系列的器件,定時(shí)器會(huì)自動(dòng)地接入到GT的輸出。 1.2 約束設(shè)置格式 主時(shí)鐘約束使用命令create_clock進(jìn)行創(chuàng)建,進(jìn)入Timing

人員定位系統(tǒng)對(duì)生產(chǎn)密集型企業(yè)的重要意義

發(fā)電、供電、石油化工、鋼鐵冶金行業(yè)為生產(chǎn)設(shè)備密集型企業(yè),生產(chǎn)現(xiàn)場(chǎng)錯(cuò)綜復(fù)雜,稍有不慎便會(huì)發(fā)生危險(xiǎn);建筑工地現(xiàn)場(chǎng)施工作業(yè)中,存在著人員流動(dòng)性大、現(xiàn)場(chǎng)狀況雜亂、安全隱患難以察覺等問題;工廠安全管理

電路的兩類約束指的是哪兩類

電路的兩類約束通常指的是電氣約束和物理約束。這兩類約束在電路設(shè)計(jì)和分析中起著至關(guān)重要的作用。 一、電氣約束 電氣

Cadence快板PCB培訓(xùn)

Allegro環(huán)境介紹Allegro環(huán)境設(shè)定 焊盤制作 元件封裝制作 電路板創(chuàng)建PCB疊層設(shè)置和網(wǎng)表導(dǎo)入 約束規(guī)則管理布局 布線 覆銅PCB設(shè)計(jì)

發(fā)表于 07-02 17:22

?0次下載

Xilinx FPGA編程技巧之常用時(shí)序約束詳解

今天給大俠帶來Xilinx FPGA編程技巧之常用時(shí)序約束詳解,話不多說,上貨。

基本的約束方法

為了保證成功的設(shè)計(jì),所有路徑的時(shí)序要求必須能夠讓執(zhí)行工具獲取。最普遍的三種路徑以及異常路徑為

發(fā)表于 05-06 15:51

時(shí)序約束實(shí)操

添加約束的目的是為了告訴FPGA你的設(shè)計(jì)指標(biāo)及運(yùn)行情況。在上面的生成約束之后,在Result àxx.sdc中提供約束參考(請(qǐng)注意該文件不能直接添加到工程中,需要熱復(fù)制到別的指定目錄或者新建自己的SDC文件添加到工程)。

Xilinx FPGA的約束設(shè)置基礎(chǔ)

LOC約束是FPGA設(shè)計(jì)中最基本的布局約束和綜合約束,能夠定義基本設(shè)計(jì)單元在FPGA芯片中的位置,可實(shí)現(xiàn)絕對(duì)定位、范圍定位以及區(qū)域定位。

發(fā)表于 04-26 17:05

?1212次閱讀

Xilinx FPGA編程技巧之常用時(shí)序約束詳解

今天給大俠帶來Xilinx FPGA編程技巧之常用時(shí)序約束詳解,話不多說,上貨。

基本的約束方法為了保證成功的設(shè)計(jì),所有路徑的時(shí)序要求必須能夠讓執(zhí)行工具獲取。最普遍的三種路徑以及異常路徑為

發(fā)表于 04-12 17:39

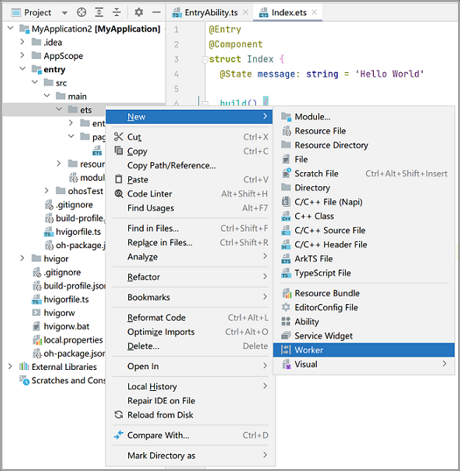

鴻蒙OS開發(fā)實(shí)例:【ArkTS類庫(kù)多線程CPU密集型任務(wù)TaskPool】

CPU密集型任務(wù)是指需要占用系統(tǒng)資源處理大量計(jì)算能力的任務(wù),需要長(zhǎng)時(shí)間運(yùn)行,這段時(shí)間會(huì)阻塞線程其它事件的處理,不適宜放在主線程進(jìn)行。例如圖像處理、視頻編碼、數(shù)據(jù)分析等。

基于多線程并發(fā)機(jī)制處理CPU密集型任務(wù)可以提高CPU利用率,提升應(yīng)用程序響應(yīng)速度。

鴻蒙OS開發(fā)實(shí)例:【ArkTS類庫(kù)多線程I/O密集型任務(wù)開發(fā)】

使用異步并發(fā)可以解決單次I/O任務(wù)阻塞的問題,但是如果遇到I/O密集型任務(wù),同樣會(huì)阻塞線程中其它任務(wù)的執(zhí)行,這時(shí)需要使用多線程并發(fā)能力來進(jìn)行解決。

I/O密集型任務(wù)的性能重點(diǎn)通常不在于CPU

博泰“車聯(lián)網(wǎng)云服務(wù)平臺(tái)”入選2023年度專利密集型產(chǎn)品名單

近日,中國(guó)專利保護(hù)協(xié)會(huì)首次組織開展了專利密集型產(chǎn)品認(rèn)定工作,并于近期發(fā)布2023年專利密集型產(chǎn)品名單,博泰的“車聯(lián)網(wǎng)云服務(wù)平臺(tái)”入選2023年度專利密集型產(chǎn)品名單。

鴻蒙原生應(yīng)用開發(fā)-ArkTS語言基礎(chǔ)類庫(kù)多線程I/O密集型任務(wù)開發(fā)

使用異步并發(fā)可以解決單次I/O任務(wù)阻塞的問題,但是如果遇到I/O密集型任務(wù),同樣會(huì)阻塞線程中其它任務(wù)的執(zhí)行,這時(shí)需要使用多線程并發(fā)能力來進(jìn)行解決。

I/O密集型任務(wù)的性能重點(diǎn)通常不在于CPU的處理

發(fā)表于 03-21 14:57

鴻蒙原生應(yīng)用開發(fā)-ArkTS語言基礎(chǔ)類庫(kù)多線程CPU密集型任務(wù)TaskPool

密集型任務(wù)可以提高CPU利用率,提升應(yīng)用程序響應(yīng)速度。

當(dāng)進(jìn)行一系列同步任務(wù)時(shí),推薦使用Worker;而進(jìn)行大量或調(diào)度點(diǎn)較為分散的獨(dú)立任務(wù)時(shí),不方便使用8個(gè)Worker去做負(fù)載管理,推薦采用

發(fā)表于 03-19 14:14

HarmonyOS CPU與I/O密集型任務(wù)開發(fā)指導(dǎo)

。 基于多線程并發(fā)機(jī)制處理CPU密集型任務(wù)可以提高CPU利用率,提升應(yīng)用程序響應(yīng)速度。 當(dāng)進(jìn)行一系列同步任務(wù)時(shí),推薦使用Worker;而進(jìn)行大量或調(diào)度點(diǎn)較為分散的獨(dú)立任務(wù)時(shí),不方便使用8個(gè)Worker去做負(fù)載管理,推薦采用TaskPool。接下來將以圖像

FPGA物理約束之布局約束

在進(jìn)行布局約束前,通常會(huì)對(duì)現(xiàn)有設(shè)計(jì)進(jìn)行設(shè)計(jì)實(shí)現(xiàn)(Implementation)編譯。在完成第一次設(shè)計(jì)實(shí)現(xiàn)編譯后,工程設(shè)計(jì)通常會(huì)不斷更新迭代,此時(shí)對(duì)于設(shè)計(jì)中一些固定不變的邏輯,設(shè)計(jì)者希望它們的編譯結(jié)果

如何創(chuàng)建和管理約束密集型、高度約束的PCB設(shè)計(jì)

如何創(chuàng)建和管理約束密集型、高度約束的PCB設(shè)計(jì)

評(píng)論