LTC2272 16 位���、65Msps 串行輸出 ADC

數(shù)據(jù):

LTC2272產(chǎn)品技術(shù)英文資料手冊

優(yōu)勢和特點

- 高速串行接口 (JESD204)

- 采樣速率:80Msps/65Msps

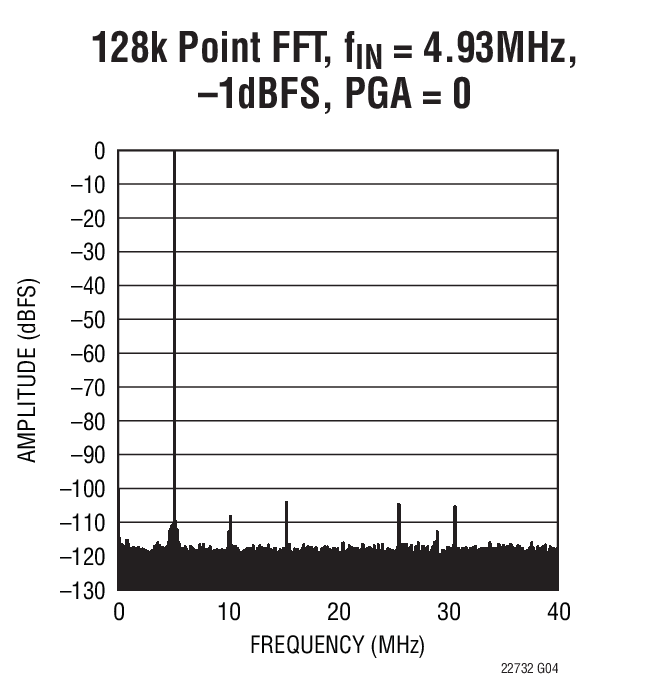

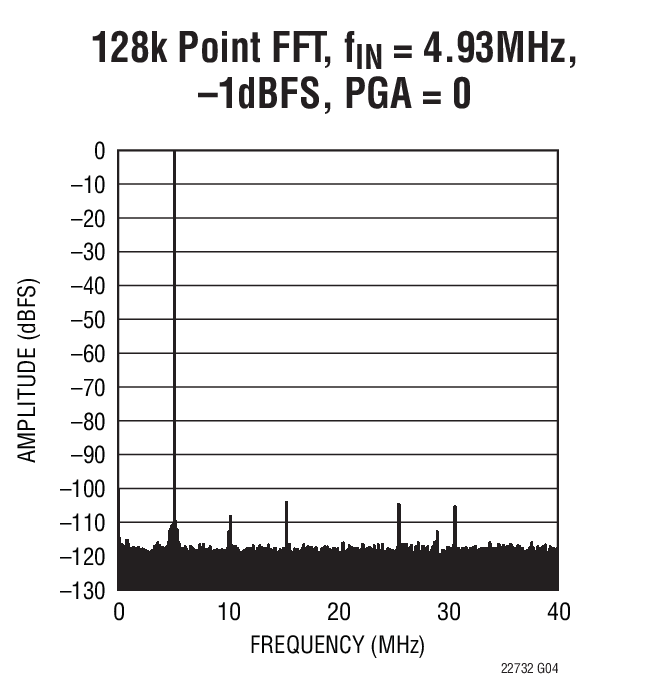

- 77.7dBFS 噪聲層

- 100dB SFDR

- 在 140MHz 頻率條件下的 SFDR > 90dB (1.5VP-P 輸入范圍)

- PGA 前端 (2.25VP-P 或 1.5VP-P 輸入范圍)

- 700MHz 滿功率帶寬 S/H (采樣及保持)

- 任選的內(nèi)部高頻顫動

- 單 3.3V 電源

- 功耗:1100mW/990mW

- 時鐘占空比穩(wěn)定器

- 引腳兼容系列

- 105Msps:LTC2274

- 80Msps:LTC2273

- 65Msps:LTC2272

- 40 引腳 6mm x 6mm QFN 封裝

?

產(chǎn)品詳情

LTC?2273/LTC2272 是 80Msps/65Msps、16 位 A/D 轉(zhuǎn)換器��,具有一個高速串行接口����。它們專為對具有一個 700MHz 輸入帶寬的高頻、寬動態(tài)范圍信號進行數(shù)字化處理而設(shè)計�。該 ADC 的輸入范圍可以采用 PGA 前端進行優(yōu)化。根據(jù)用于數(shù)據(jù)轉(zhuǎn)換器的 JEDEC 串行接口規(guī)范 (JESD204) 對輸出數(shù)據(jù)進行串行化處理����。

LTC2273/LTC2272 非常適合于那些希望把敏感的模擬電路與噪聲數(shù)字邏輯電路隔離開來的苛刻應(yīng)用����。其 AC 性能包括 77.7dB 噪聲層和 100dB 無寄生動態(tài)范圍 (SFDR)。80fs RMS 的超低內(nèi)部抖動實現(xiàn)了高輸入頻率的欠采樣和卓越的噪聲性能�����。最大 DC 規(guī)格包括在整個溫度范圍內(nèi)的 ±4.5LSB INL 和 ±1LSB DNL (無漏失碼)��。

可以利用一個正弦波�����、PECL、LVDS����、TTL 或 CMOS 輸入對編碼時鐘輸入、ENC+ 和ENC– 進行差分或單端驅(qū)動���。一個時鐘占空比穩(wěn)定器在全速和各種時鐘占空比條件下實現(xiàn)了高性能��。

?

應(yīng)用

- 電信

- 接收機

- 蜂窩基站

- 頻譜分析

- 成像系統(tǒng)

- ATE

方框圖