FIFO的深度應(yīng)該怎么計(jì)算

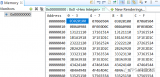

FIFO是FPGA/IC設(shè)計(jì)中經(jīng)常使用到的模塊,它經(jīng)常被用在兩個(gè)模塊之間進(jìn)行數(shù)據(jù)的緩存,以避免數(shù)據(jù)在....

JPEG LS算法局部梯度值計(jì)算原理

如果同一個(gè)上下文中對(duì)少量元素進(jìn)行編碼,通常無(wú)法獲得足夠的上下文編碼信息。但是如果對(duì)大量元素進(jìn)行編碼又....

以太網(wǎng)自協(xié)商機(jī)制—雙絞線自協(xié)商案例(四)

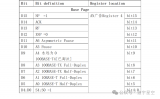

10M/100M/1000M自協(xié)商,主要協(xié)商的內(nèi)容為“速度雙工”、“流控”和“主從”三大類,下面先介....

以太網(wǎng)自協(xié)商機(jī)制-雙絞線自協(xié)商案例設(shè)計(jì)(三)

NextPage有兩大類(D13=1時(shí)為Messgage Page; D13=0時(shí)為Unformat....

基于IEEE Clause 28雙絞線的以太網(wǎng)自協(xié)商機(jī)制解析(一)

自協(xié)商機(jī)制是以太網(wǎng)技術(shù)物理層重要的一種機(jī)制。它可以使得不同底層技術(shù)網(wǎng)絡(luò)設(shè)備(計(jì)算機(jī)終端,網(wǎng)橋,交換機(jī)....

為什么不能直接對(duì)RGB圖做直方圖均衡化

相信好多人在開(kāi)始學(xué)習(xí)FPGA圖像處理的時(shí)候都是接觸的RGB轉(zhuǎn)灰度圖,Sobel圖像檢測(cè),直方圖均衡化....

Vivado 2023.2版本的新增功能

Vivado在前一段時(shí)間更新了2023.2版本,經(jīng)過(guò)一段時(shí)間的使用這個(gè)版本還是很絲滑的,用起來(lái)挺舒服....

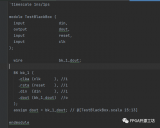

verilog中數(shù)據(jù)的符號(hào)屬性(有符號(hào)數(shù)和無(wú)符號(hào)數(shù))探究根源

為了省流,還是先甩結(jié)論。有符號(hào)數(shù)和無(wú)符號(hào)數(shù)的最本質(zhì)區(qū)別就是:符號(hào)位的識(shí)別和高位拓展。除此之外,另一個(gè)....

Canny雙閾值邊緣檢測(cè)和弱邊緣連接詳解

在上一篇FPGA圖像處理--Canny邊緣檢測(cè)(一)里介紹了Canny邊緣檢測(cè)的NMS計(jì)算,這里就介....

FPGA圖像處理之Canny邊緣檢測(cè)

在邊緣檢測(cè)算法里面Sobel是比較簡(jiǎn)單的一個(gè)算法,但是其檢測(cè)出來(lái)的邊緣往往是比較粗的,效果不是很好,....

FPGA圖像處理--高斯模糊(二)

在仿真的時(shí)候會(huì)實(shí)時(shí)打印DUT和參考模型的結(jié)果是否比對(duì)成功。因?yàn)樵O(shè)置了DUT和參考模型的結(jié)果之間的閾值....

spinalhdl轉(zhuǎn)Verilog可讀性 SpinalHDL開(kāi)發(fā)流程

SpinalHDL是基于Scala全新的硬件描述語(yǔ)言,解決了不少Verilog等傳統(tǒng)HDL語(yǔ)言的痛點(diǎn)....

如何在FPGA中實(shí)現(xiàn)RGB轉(zhuǎn)HSV

HSV色彩空間相對(duì)于RGB色彩空間更適合做顏色追蹤,分割顏色等。那么RGB色彩空間要怎么轉(zhuǎn)變?yōu)镠SV....

Vitis調(diào)試技巧-從Vitis中導(dǎo)出數(shù)據(jù)到本地

在Zynq開(kāi)發(fā)中有一個(gè)很常用的功能是將ARM端的數(shù)據(jù)導(dǎo)出到本地,然后通過(guò)Matlab,Python等....

Xilinx FPGA重構(gòu)技術(shù)介紹

重構(gòu)技術(shù)是一項(xiàng)非常實(shí)用的技術(shù),從比特屬性上來(lái)分類可以分成全部重構(gòu)和局部重構(gòu)。

從RTL追蹤到Scala

在三天前SpinalHDL1.8.0正式上線,在這次更新中增加了Scala代碼和生成的RTL代碼....