Verilog HDL的基礎(chǔ)知識

本文繼續(xù)介紹Verilog HDL基礎(chǔ)知識,重點(diǎn)介紹賦值語句、阻塞與非阻塞、循環(huán)語句、同步與異步、函....

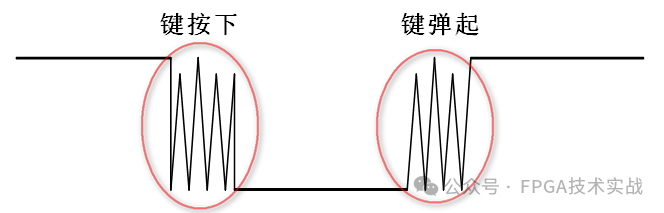

基于FPGA實(shí)現(xiàn)按鍵消抖處理

引言: 按鍵在電子產(chǎn)品中經(jīng)常用到,由于按鍵的機(jī)械特性,按鍵在閉合或松開的瞬間伴隨著一連串的抖動,這樣....

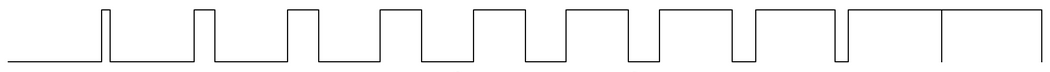

呼吸燈的概念和實(shí)現(xiàn)原理

呼吸燈在日常生活中經(jīng)常見到,如電子時(shí)鐘,小夜燈等等,本文我們介紹下通過PWM波來控制LED燈,實(shí)現(xiàn)呼....

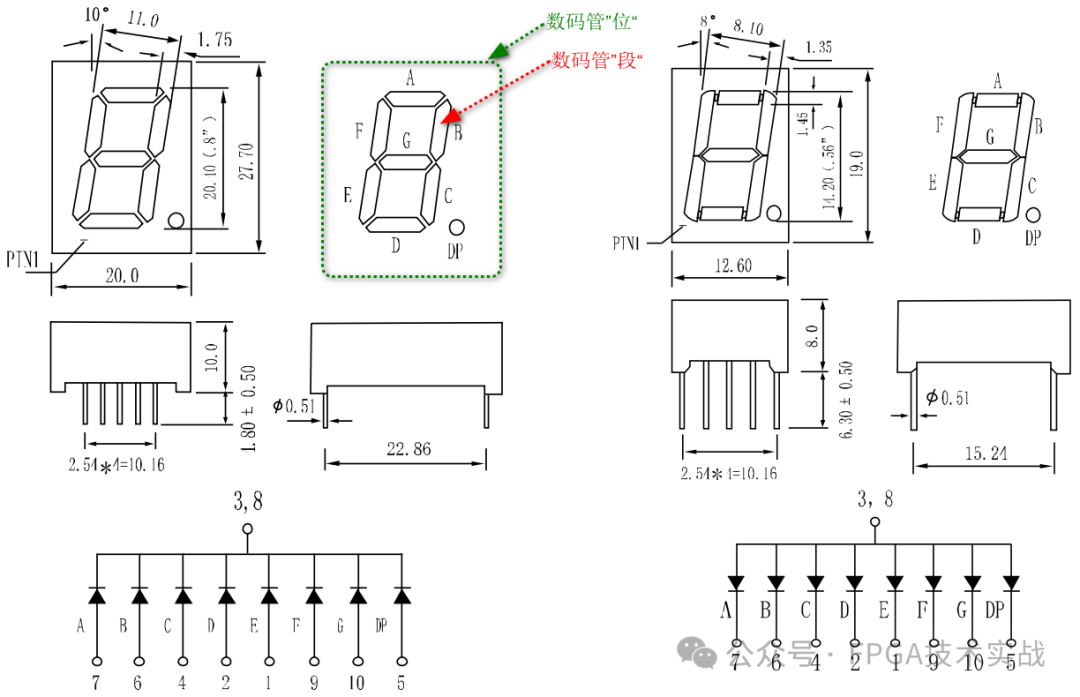

基于FPGA實(shí)現(xiàn)數(shù)碼管顯示

本文介紹數(shù)碼管顯示譯碼基本工作原理及Verilog HDL驅(qū)動代碼編寫,進(jìn)一步熟練掌握FPGA入門基....

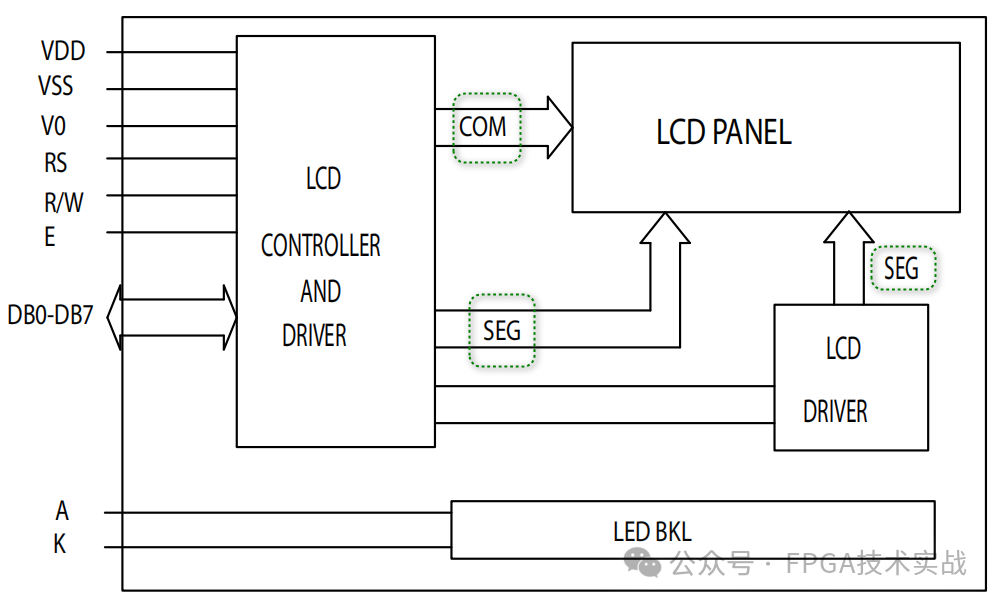

基于FPGA的LCD1602液晶顯示模塊驅(qū)動設(shè)計(jì)

本文通過以LCD1602液晶顯示模塊為基礎(chǔ),介紹FPGA驅(qū)動LCD1602原理,詳細(xì)介紹硬件原理圖設(shè)....

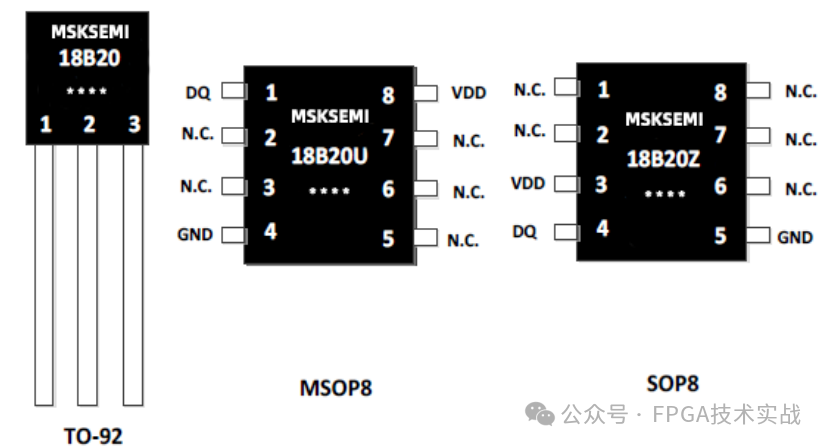

DS18B20溫度傳感器的工作原理和硬件設(shè)計(jì)

通過本文可以了解DS18B20溫度傳感器工作原理、硬件設(shè)計(jì)、DS18B20單總線接口驅(qū)動編寫。

Xilinx FPGA BGA推薦設(shè)計(jì)規(guī)則和策略(二)

工程師必須在設(shè)計(jì)階段早期評估功率需求,以確保有足夠的層和面積為需要功率的BGA焊盤提供足夠的功率。

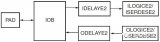

Xilinx SelectIO資源內(nèi)部的IDELAYE2應(yīng)用介紹

本文我們介紹下Xilinx SelectIO資源內(nèi)部IDELAYE2資源應(yīng)用。IDELAYE2原句配....

Vivado編譯常見錯(cuò)誤與關(guān)鍵警告梳理與解析

Xilinx Vivado開發(fā)環(huán)境編譯HDL時(shí),對時(shí)鐘信號設(shè)置了編譯規(guī)則,如果時(shí)鐘由于硬件設(shè)計(jì)原因分....

XC7K410T-FFG900外設(shè)之DDR3硬件設(shè)計(jì)方案分享

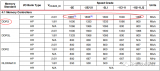

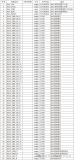

在數(shù)據(jù)速率帶寬約束方面,DDR3運(yùn)行速度受限于其與K7-410T FPGA互聯(lián)的I/O Bank 管....

基于Xilinx K7-410T的高速DAC之AD9129開發(fā)筆記(二)

上一篇文章我們簡單介紹了AD9129的基礎(chǔ)知識,包括芯片的重要特性,外部接口相關(guān)的信號特性等。本篇我....

基于Xilinx K7-410T的高速DAC之AD9129開發(fā)筆記

引言:從本文開始,我們介紹下項(xiàng)目中設(shè)計(jì)的并行LVDS高速DAC接口設(shè)計(jì),包括DAC與FPGA硬件接口....

基于TXS0108實(shí)現(xiàn)FPGA IO Bank接不同外設(shè)IO接口電壓轉(zhuǎn)換

引言:上一篇文章我們介紹了通過添加電阻器、場效應(yīng)晶體管(FET)開關(guān)、電平轉(zhuǎn)換器甚至其他Xilinx....

串行配置和并行配置模式下的多片F(xiàn)PGA配置數(shù)據(jù)流加載方式

在需要多個(gè)FPGA芯片的應(yīng)用中,如果JTAG鏈上所有FPGA采用相同配置,可以通過“成組”加載方式同....

提高Xilinx FPGA Flash下載速度

最近在編寫完FPGA邏輯,成功生成.bin文件后,發(fā)現(xiàn)將數(shù)據(jù)流文件燒寫到Flash時(shí)間過長,突然想起....

Matlab算法映射至FPGA硬件邏輯

引言:本文分享一篇技術(shù)PPT,該P(yáng)PT主要介紹如何將算法映射到FPGA或ASIC硬件架構(gòu)。