聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

ARM

+關(guān)注

關(guān)注

134文章

9169瀏覽量

369225 -

中國(guó)芯

+關(guān)注

關(guān)注

19文章

277瀏覽量

32425

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Microarchitecture指令集體系結(jié)構(gòu)

第二章 ARM微處理器概述與編程模型ARM體系結(jié)構(gòu)及其發(fā)展歷史處理器的體系結(jié)構(gòu)處理器微架構(gòu) Microarchitecture指令集體系結(jié)構(gòu) Architecture幾種常見的指令集X86Inter

發(fā)表于 12-14 07:13

了解體系結(jié)構(gòu) - 介紹 Arm 體系結(jié)構(gòu)

。該體系結(jié)構(gòu)為軟件開發(fā)人員公開了一個(gè)通用的指令集和工作流程,也稱為程序員模型。這有助于確保架構(gòu)的不同實(shí)現(xiàn)之間的互操作性,以便軟件可以在不同的 Arm 設(shè)備上運(yùn)行。本指南為任何對(duì)此感興趣的人介紹了 Arm

發(fā)表于 08-01 14:35

Arm的DRTM體系結(jié)構(gòu)規(guī)范

本規(guī)范定義了基于Arm A配置文件體系結(jié)構(gòu)的處理器的動(dòng)態(tài)測(cè)量信任根(DRTM)體系結(jié)構(gòu)。本規(guī)范基于TCG D-RTM體系結(jié)構(gòu)[4]的概念,但作為一個(gè)獨(dú)立的獨(dú)立文檔發(fā)揮作用。它使用了TC

發(fā)表于 08-08 07:45

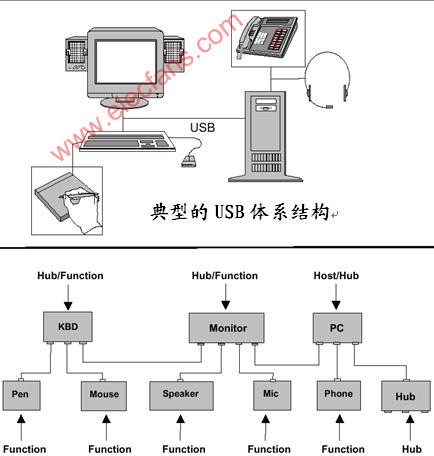

USB體系結(jié)構(gòu)概述

USB體系結(jié)構(gòu)概述

本章主要內(nèi)容是關(guān)于USB的概述和一些關(guān)鍵的概念。USB是一種電纜總線,支持在主機(jī)和各式各樣的即插即

發(fā)表于 04-15 20:43

?1963次閱讀

LTE體系結(jié)構(gòu)

LTE體系結(jié)構(gòu)

LTE體系結(jié)構(gòu)可以借助SAE 體系結(jié)構(gòu)來(lái)做詳細(xì)描述。在SAE 體系結(jié)構(gòu)中,RNC部分功能、GGSN、SGSN 節(jié)點(diǎn)將被融合為一

發(fā)表于 06-16 13:09

?9875次閱讀

網(wǎng)絡(luò)體系結(jié)構(gòu),什么是網(wǎng)絡(luò)體系結(jié)構(gòu)

網(wǎng)絡(luò)體系結(jié)構(gòu),什么是網(wǎng)絡(luò)體系結(jié)構(gòu)

通過(guò)通信信道和設(shè)備互連起來(lái)的多個(gè)不同地理位置的計(jì)算機(jī)系統(tǒng),要使其能協(xié)同工作實(shí)現(xiàn)信息交換和資源共享

發(fā)表于 04-06 16:30

?1725次閱讀

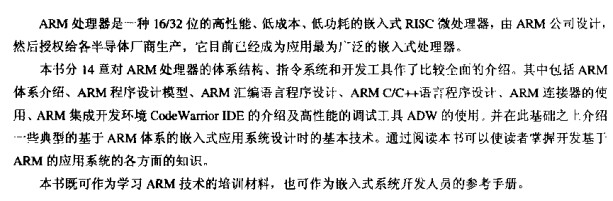

ARM體系結(jié)構(gòu)與程序設(shè)計(jì)

《ARM體系結(jié)構(gòu)與程序設(shè)計(jì)》是ARM體系結(jié)構(gòu)與程序設(shè)計(jì)的一本實(shí)用指導(dǎo)書籍,通過(guò)案例詳細(xì)介紹了ARM體系結(jié)構(gòu)與程序設(shè)計(jì),案例中的程序都取自實(shí)際的項(xiàng)目,且對(duì)程序有詳細(xì)注解。

發(fā)表于 10-27 16:37

?2378次閱讀

軟件體系結(jié)構(gòu)的分析

軟件系統(tǒng)因具有節(jié)點(diǎn)眾多、節(jié)點(diǎn)間聯(lián)系復(fù)雜、隨時(shí)間演化、自組織臨界等特性可將其視為復(fù)雜系統(tǒng)。在軟件安全領(lǐng)域,對(duì)軟件體系結(jié)構(gòu)的分析一直是研究的重點(diǎn)。軟件體系結(jié)構(gòu)具有自身的脆性,這體現(xiàn)在軟件系統(tǒng)的運(yùn)行過(guò)程

發(fā)表于 11-24 10:34

?15次下載

基于DoDAF的衛(wèi)星應(yīng)用信息鏈體系結(jié)構(gòu)

針對(duì)偵察衛(wèi)星應(yīng)用信息鏈體系結(jié)構(gòu)建模問(wèn)題,提出了基于DoDAF (department of defense architect framework)的體系結(jié)構(gòu)描述方法和基于ABM (activity

發(fā)表于 01-10 16:58

?1次下載

一場(chǎng)關(guān)于ARM——數(shù)字世界的體系結(jié)構(gòu)的演講

演講題目:ARM - The Architecture for The Digital World;演講人:馮成ARM公司高級(jí)戰(zhàn)略業(yè)務(wù)發(fā)展經(jīng)理

在英特爾體系結(jié)構(gòu)源代碼上下載并編譯Android

本視頻演示如何在英特爾體系結(jié)構(gòu)源代碼上下載并編譯Android。

微處理器體系結(jié)構(gòu)

《微處理器體系結(jié)構(gòu)》適合作為高等院校集成電路設(shè)計(jì)相關(guān)專業(yè)工程碩士的教材,并可以作為微處理器硬件與軟件設(shè)計(jì)相關(guān)專業(yè)高年級(jí)本科生和研究生的教材。

《微處理器體系結(jié)構(gòu)》是一本系統(tǒng)介紹各種類型微處理器

發(fā)表于 04-14 10:29

?0次下載

Oracle體系結(jié)構(gòu)講解

Oracle體系結(jié)構(gòu)講解(開關(guān)電源技術(shù)的節(jié)能意義)-該文檔為Oracle體系結(jié)構(gòu)講解文檔,是一份十分不錯(cuò)的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,,,,,

發(fā)表于 09-27 10:27

?3次下載

一場(chǎng)關(guān)于Android的體系結(jié)構(gòu)的演講

一場(chǎng)關(guān)于Android的體系結(jié)構(gòu)的演講

評(píng)論