聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21738瀏覽量

603463

發(fā)布評論請先 登錄

相關(guān)推薦

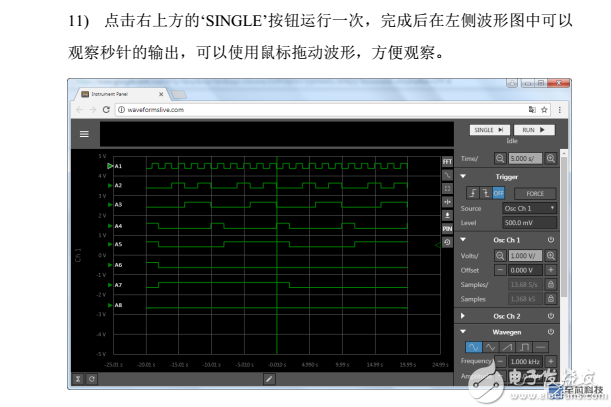

基于FPGA顯示數(shù)字鐘

用Verilog HDL語言實(shí)現(xiàn),通過VGA在LCD顯示針式數(shù)字鐘,像windows右下角 日期和時(shí)間 屬性那個(gè)鐘那樣。我想問的是如何從RAM里讀取各個(gè)圖片然后顯示出來,或通過改變圖片屬性來達(dá)到每秒刷新一下各針的位置

發(fā)表于 09-25 09:31

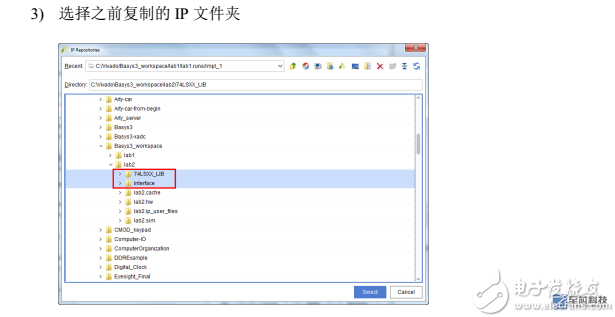

基于FPGA vivado 17.2 的數(shù)字鐘設(shè)計(jì)

基于FPGA vivado 17.2 的數(shù)字鐘設(shè)計(jì)目的:熟悉vivado 的開發(fā)流程以及設(shè)計(jì)方法附件:

發(fā)表于 12-13 10:16

基于FPGA Vivado的流水燈樣例設(shè)計(jì)資料分享

【流水燈樣例】基于 FPGA Vivado 的數(shù)字鐘設(shè)計(jì)前言模擬前言Vivado 設(shè)計(jì)流程指導(dǎo)手冊——2013.4密碼:5txi模擬

發(fā)表于 02-07 08:02

基于FPGA設(shè)計(jì)實(shí)現(xiàn)一個(gè)多功能數(shù)字鐘相關(guān)資料分享

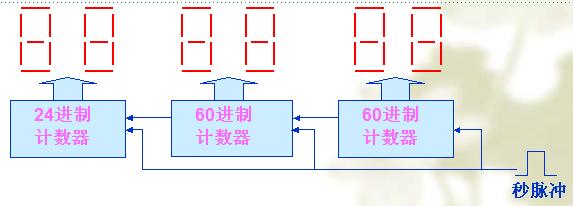

1、基于FPGA設(shè)計(jì)實(shí)現(xiàn)一個(gè)多功能數(shù)字鐘在FPGA中設(shè)計(jì)實(shí)現(xiàn)一個(gè)多功能數(shù)字鐘,具備以下功能:準(zhǔn)確計(jì)時(shí)。能顯示時(shí)、分、秒,小時(shí)的計(jì)時(shí)為24進(jìn)制,分和秒的計(jì)時(shí)為60進(jìn)制。校時(shí)功能。時(shí)、分可

發(fā)表于 07-08 17:26

基于 FPGA Vivado 的數(shù)字鐘設(shè)計(jì)(附源工程)

今天給大俠帶來基于 FPGA Vivado 的數(shù)字鐘設(shè)計(jì),開發(fā)板實(shí)現(xiàn)使用的是Digilent basys 3。話不多說,上貨。

需要源工程可以在以下資料獲取里獲取。

資料匯總|FPGA

發(fā)表于 08-18 21:18

多功能數(shù)字鐘的設(shè)計(jì)與實(shí)現(xiàn)

多功能數(shù)字鐘的設(shè)計(jì)與實(shí)現(xiàn)一、實(shí)驗(yàn)?zāi)康?nbsp;1.掌握數(shù)字鐘的設(shè)計(jì)原理。 2.用微機(jī)實(shí)驗(yàn)平臺實(shí)現(xiàn)數(shù)字鐘。 3.分析比較微機(jī)實(shí)現(xiàn)的數(shù)字鐘和其他方法實(shí)現(xiàn)的數(shù)

發(fā)表于 05-03 11:38

?477次下載

基于FPGA和Quartus II的多功能數(shù)字鐘設(shè)計(jì)與實(shí)現(xiàn)

本文以FPGA平臺為基礎(chǔ),在QuartusⅡ開發(fā)環(huán)境下設(shè)計(jì)開發(fā)多功能數(shù)字鐘。數(shù)字鐘實(shí)現(xiàn)計(jì)時(shí)\校時(shí)\整點(diǎn)報(bào)時(shí)\世界時(shí)鐘功能.

發(fā)表于 12-18 11:51

?3.7w次閱讀

華清遠(yuǎn)見FPGA代碼-基于NIOSII處理器的數(shù)字鐘設(shè)計(jì)

華清遠(yuǎn)見FPGA代碼-基于NIOSII處理器的數(shù)字鐘設(shè)計(jì)

發(fā)表于 10-27 18:07

?14次下載

基于fpga的數(shù)字鐘設(shè)計(jì)的兩款方案(含程序)

以FPGA平臺為基礎(chǔ),采用VHDL語言在QuartusⅡ開發(fā)環(huán)境下設(shè)計(jì)開發(fā)多功能數(shù)字鐘,具有計(jì)時(shí)、校時(shí)、蜂鳴鬧鈴的功能.

發(fā)表于 11-07 12:01

?3.2w次閱讀

fpga數(shù)字鐘介紹_fpga數(shù)字鐘設(shè)計(jì)

數(shù)字鐘實(shí)際上是一個(gè)對標(biāo)準(zhǔn)頻率(1HZ)進(jìn)行計(jì)數(shù)的計(jì)數(shù)電路。由于計(jì)數(shù)的起始時(shí)間不可能與標(biāo)準(zhǔn)時(shí)間(如北京時(shí)間)一致,故需要在電路上加一個(gè)校時(shí)電路,同時(shí)標(biāo)準(zhǔn)的1HZ時(shí)間信號必須做到準(zhǔn)確穩(wěn)定,通常使用石英晶體振蕩器電路構(gòu)成數(shù)字鐘。

發(fā)表于 01-15 15:37

?1.1w次閱讀

【FPGA Vivado】基于 FPGA Vivado 的流水燈樣例設(shè)計(jì)

【流水燈樣例】基于 FPGA Vivado 的數(shù)字鐘設(shè)計(jì)前言模擬前言Vivado 設(shè)計(jì)流程指導(dǎo)手冊——2013.4密碼:5txi模擬

發(fā)表于 12-04 13:21

?26次下載

FPGA多功能數(shù)字鐘系統(tǒng)原理

FPGA(可編程邏輯門陣列)是一種集成電路芯片,具有可編程的數(shù)字邏輯功能。多功能數(shù)字鐘系統(tǒng)利用FPGA技術(shù)實(shí)現(xiàn)了時(shí)鐘的顯示、計(jì)時(shí)、報(bào)時(shí)等功能。本文將詳細(xì)介紹

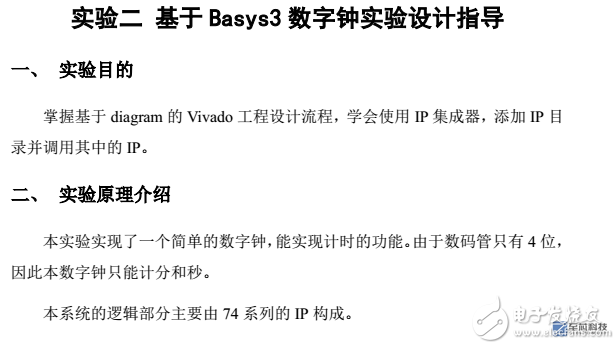

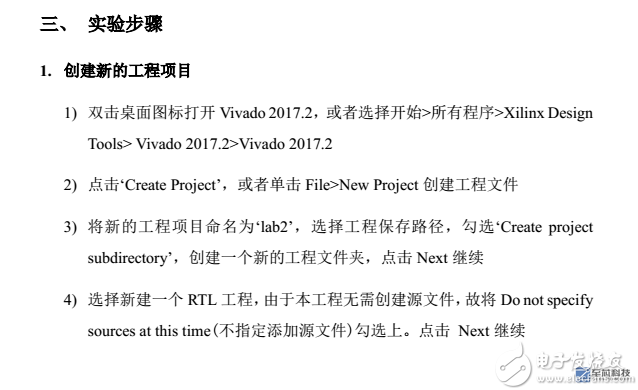

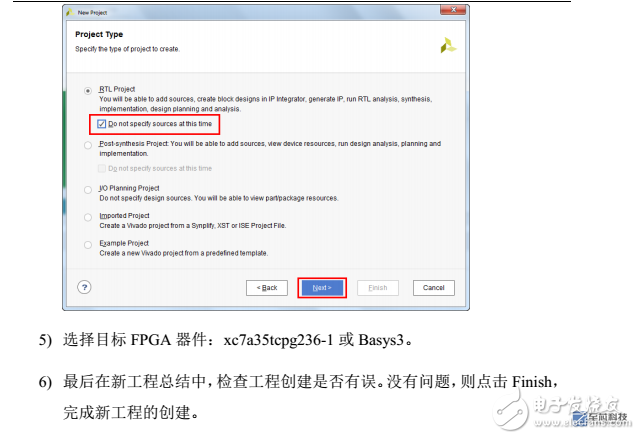

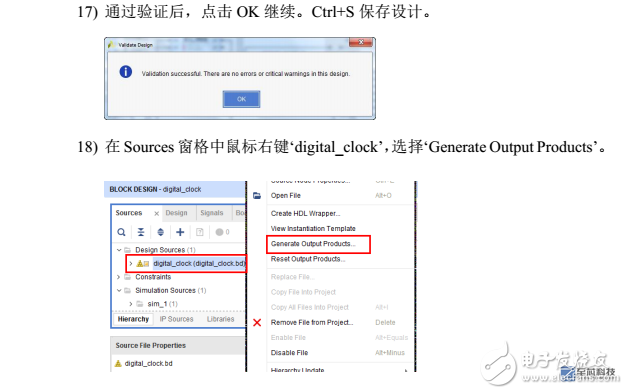

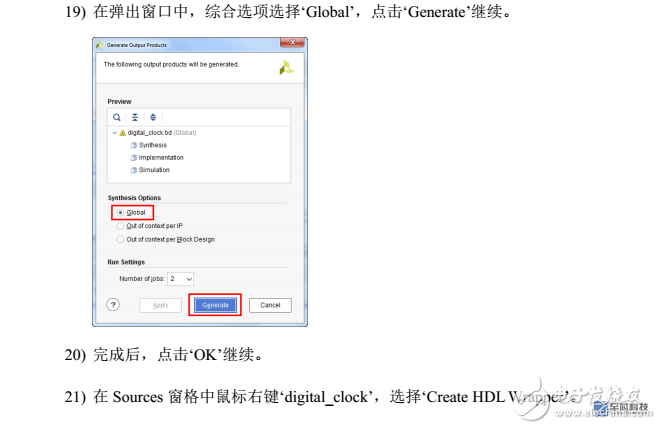

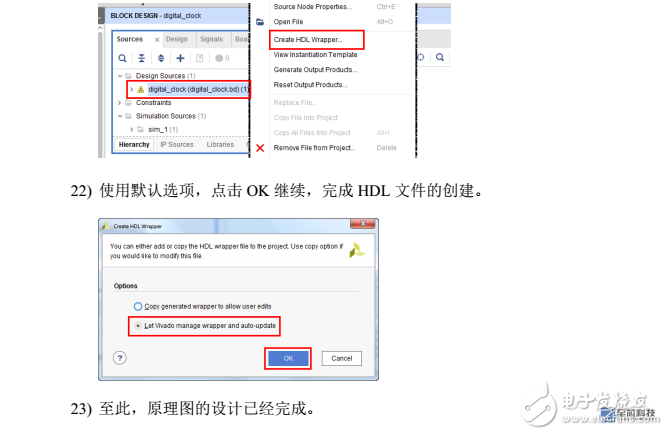

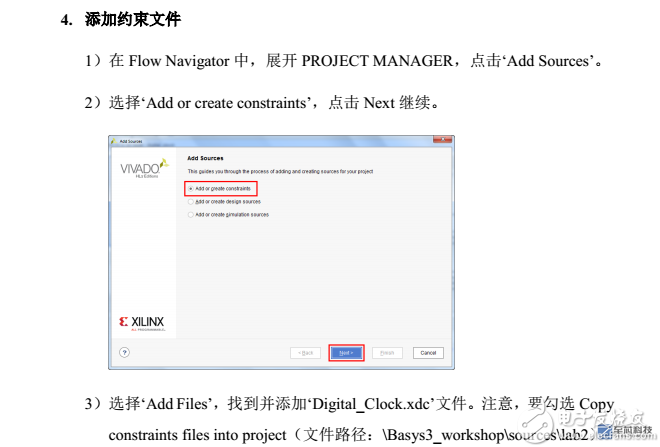

基于FPGA vivado 17.2 的數(shù)字鐘設(shè)計(jì)

基于FPGA vivado 17.2 的數(shù)字鐘設(shè)計(jì)

評論